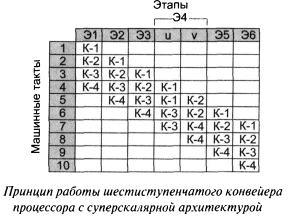

Процесор, побудований за суперскалярной архітектурі, має 2 (або більше) конвеєра для виконання команд. Це дозволяє одночасно виконувати 2 (або більше) команди. Щоб краще зрозуміти доцільність застосування суперскалярной архітектури в процесорі, давайте розглянемо попередній приклад конвеєрної обробки, в якому ми для спрощення припускали, що етап виконання команди (Е4) триває всього 1 машинний такт. А що ж станеться, якщо етап виконання команди Е4 триває 2 машинних такту? Тоді в роботі конвеєра виникнуть збої, як показано на малюнку.

Процесор не зможе перейти до фази виконання Е4 команди K2, поки він повністю не завершить фазу виконання команди K1. В результаті цикл виконання команди К-2 збільшиться на 1 машинний такт, тобто на час очікування звільнення конвеєра на етапі Е4. У міру надходження на конвеєр додаткових команд, деякі його ступені будуть працювати вхолосту (на малюнку вони виділені сірим кольором).

Для боротьби з простоями устаткування використовуються нескольео конвеййеров. У процесорі Intel Pentium було застосовано 2 конвеєра. Він став першим процесором сімейства IA-32, побудованим за суперскалярной архітектурі. У процесорі Pentium Рго вперше було застосовано 3 конвеєра.

Продовжимо розгляд нашого прикладу шестиступенчатого конвеєра і введемо в нього еше один (тобто другий) конвеєр. Як і раніше ми будемо припускати, що фаза виконання команди Е4 триває 2 машинних такту. Як показано на малюнку, команда з непарним номером надходить на u-конвеєр, а команда з парним номером - на v-конвеєр. Подібний підхід дозволяє ліквідувати простої в роботі конвеєра.

У МП з такою архітектурою застосовується розпаралелювання виконання команд між декількома конвеєрами, причому рішення про паралельне виконання команд приймається апаратурою процесора на етапі виконання. Ефективне використання такої архітектури вимагає спеціальної оптимізації машинного коду в компіляторі для генерації пар незалежних команд (коли результат однієї команди не є аргументом іншої).

Суперскалярні МП можуть видавати на виконання в кожному такті змінне число команд, і робота їх конвеєрів може плануватися як статично за допомогою компілятора, так і за допомогою апаратних засобів динамічної оптимізації. Суперскалярні машини використовують паралелізм на рівні команд шляхом посилки декількох команд із звичайного потоку команд в кілька функціональних пристроїв.

У типовій суперскалярной машині апаратура може здійснювати видачу від 1 до 8 команд в одному такті. Зазвичай ці команди повинні бути незалежними і задовольняти деяким обмеженням, наприклад таким, що в кожному такті не може видаватися більше однієї команди звернення до пам'яті. Якщо будь-яка команда в потоці команд є логічно залежною або не задовольняє критеріям видачі, на виконання будуть видані тільки команди, що передують даній. Тому швидкість видачі команд в суперскалярні машинах є змінною

АрхітектуриCisc

архітектури risc

MCS-51 (Intel 8051) - класична архітектура мікроконтролера. Для неї існує крос-асемблер ASM51, випущений корпорацією MetaLink.

Крім того, багато фірм - розробники програмного забезпечення, такі як IAR або Keil, представили свої варіанти ассемблеров. У ряді випадків застосування цих ассемблеров виявляється більш ефективним завдяки зручному набору директив і наявності середовища програмування, що об'єднує в собі професійний асемблер і мову програмування Сі, відладчик і менеджер програмних проектів.

На даний момент існують 2 компілятора виробництва Atmel (AVRStudio 3 і AVRStudio4). Друга версія - спроба виправити не надто вдалу першу.

В рамках проекту AVR-GCC (він же WinAVR) існує компілятор avr-as (це портований під AVR асемблер GNU as ізGCC).

Також існує вільний мінімалістичний компілятор avra [1].