Для того щоб повністю розібратися з Two-Wire Interface (TWI). пишемо з нуля в AVR STUDIO процедури ініціалізації, читання і запису. Детально зупиняємося на кожному кроці і розбираємося. Потім Промоделюємо все в Proteus.

Апаратний модуль TWI і протокол I2C

У мікроконтролери серії MEGA входить модуль TWI, за допомогою якого ми будемо працювати з шиною I2C. Модуль TWI по суті є посередником між нашою програмою і підключається пристроєм (пам'ять I2C EEPROM, наприклад).

Структура модуля TWI в мікроконтролерах AVR

Шина I2C складається з двох проводів:

- SCL (Serial Clock Line) - лінія послідовної передачі тактовихімпульсів.

- SDA (Serial Data Line) - лінія послідовної передачі даних.

До цієї шині ми можемо одночасно підключити до 128 мікросхем.

Підключення до шини TWI

Як видно на блок-схемі, TWI умовно складається з чотирьох блоків. Спочатку нам потрібно буде налаштувати Генератор швидкості зв'язку, і ми відразу забудемо про нього. Основна робота - з Блоком управління.

Отже, наше завдання зараз розібратися з регістрами, що входять в Генератор швидкості зв'язку та Блок управління:

Регістр швидкості зв'язку TWBR

Регістр управління TWCR

Регістр статусу (стану) TWSR

Регістр даних TWDR

І все, розібравшись всього лише з 4-ма регістрами, ми зможемо повноцінно працювати із зовнішньою пам'яттю EEPROM і взагалі, обмінюватися даними по I2C з будь-яким іншим пристроєм.

Генератор швидкості зв'язку та Регістр швидкості зв'язку TWBR

Блок генератора швидкості зв'язку управляє лінією SCL, а саме періодом тактових імпульсів. Управляти лінією SCL може тільки ведучий. Період SCL управляється шляхом установки регістра швидкості зв'язку TWI (TWBR) і біт предделителя в регістрі статусу TWI (TWSR).

Частота SCL генерується за такою формулою:

- TWBR - значення в регістрі швидкості зв'язку TWI;

- TWPS - значення біт предделителя в регістрі статусу TWI (TWSR).

- Fцпу - тактова частота ведучого

- FSCL - частота тактових імпульсів лінії SCL

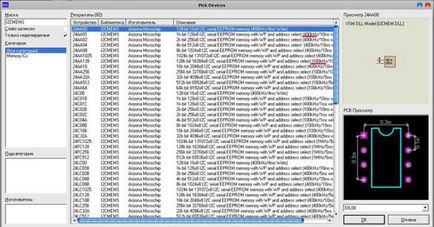

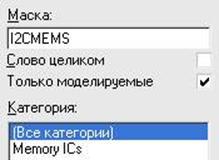

Налаштування TWBR потрібна, тому що ведена мікросхема навчена обмінюватися даними на певній частоті. Наприклад, в Proteus, введіть в пошук I2CMEM, побачите велику кількість мікросхем пам'яті, в основному у них вказані частоти 100 і 400Khz.

Ну ось, підставляючи в формулу частоти FЦПУ і FSCL. ми зможемо знайти оптимальне значення для регістра TWBR.

TWPS - це 2-бітове число [TWPS1: TWPS0], перший біт - це розряд TWPS0, другий - TWPS1 в регістрі статусу TWSR. Ставлячи Переддільник швидкості зв'язку 4 TWPS. ми можемо знижувати значення TWBR (тому що TWBR - це байт, максимальне значення 255). Але зазвичай це не потрібно, тому TWPS зазвичай задається 0 і 4 TWPS = 1. Набагато частіше, навпаки, ми впираємося в нижній діапазон регістра TWBR. Якщо TWI працює в провідному режимі, то значення TWBR має бути не менше 10. Якщо значення TWBR менше 10, то ведучий пристрій шини може генерувати некоректні сигнали на лініях SDA і SCL під час передачі байта.

Розряд 7 - TWINT: Прапор переривання TWI

Цей прапор встановлюється апаратно, якщо TWI завершує поточне завдання (наприклад, передачу, прийняття даних) і очікує реакції програми. Лінія SCL залишається в низькому стані, поки встановлений прапор TWINT. Прапор TWINT скидається програмно шляхом запису в нього логічної 1. Очищення даного прапора призводить до відновлення роботи TWI, тобто програмний скидання даного прапора необхідно виконати після завершення опитування регістрів статусу TWSR і даних TWDR.

Розряд 6 - TWEA: Біт дозволу підтвердження

Біт TWEA управляє генерацією імпульсу підтвердження. Як видно в таблиці, за замовчуванням він скинутий. Зупинятися на ньому не буду, він в даній статті не знадобиться.

Розряд 5 - TWSTA: Біт умови СТАРТ

Ми повинні встановити даний біт при необхідності стати провідним на шині I2C. TWI апаратно перевіряє доступність шини і генерує умова СТАРТ, якщо шина вільна. Ми перевіряємо цю умову (по регістру статусу, буде далі) і якщо шина вільна, то ми можемо починати з нею працювати. Інакше потрібно буде почекати, поки шина звільниться.

Розряд 4 - TWSTO: Біт умови СТОП

Установка біта TWSTO в режимі ведучого призводить до генерації умови СТОП на шині I2C. Якщо на шині виконується умова СТОП, то біт TWSTO скидається автоматично і шина звільняється.

Розряд 3 - TWWC: Прапор помилкового запису

Біт TWWC встановлюється при спробі запису в регістр даних TWDR, коли TWINT має низький рівень. Прапор скидається при записі регістра TWDR, коли TWINT = 1.

Розряд 2 - TWEN: Біт дозволу роботи TWI

Біт TWEN дозволяє роботу TWI і активізує інтерфейс TWI. Якщо біт TWEN встановлений, то TWI бере на себе функції управління лініями введення-виведення SCL і SDA. Якщо даний біт дорівнює нулю, то TWI відключається і все передачі припиняються незалежно від стану роботи.

Розряд 1 - Резервний біт

Розряд 0 - TWIE: Дозвіл переривання TWI

Якщо в даний біт записана балка. 1 і встановлений біт I в регістрі SREG (переривання дозволені глобально), то дозволяється переривання від модуля TWI (ISR (TWI_vect)) при будь-якій зміні регістра статусу.

Регістр стану TWI - TWSR

У режимі передавача регістр TWDR містить байт для передачі. У режимі приймача регістр TWDR містить останній прийнятий байт. Будьте уважні, після апаратної установки прапора TWINT, регістр TWDR не містить нічого певного.

Всі функції (ініціалізація TWI, читання, запис зовнішньої пам'яті) я винесу в окремі файли, як це і прийнято робити, i2c_eeprom.c і i2c_eeprom.h.

Ну ось, найголовніші функції ми написали. На цій базі можна написати функції для читання \ запису масиву байтів. Також можна додати переривання ISR (TWI_INT), яке буде спрацьовувати при кожній зміні регістра статусу. Я скажу тільки пару слів про це, оскільки розібравшись в вищевикладеному, вам не складе труднощів реалізувати їх самому.

будуть наступними, частина коду затягує в цикл:

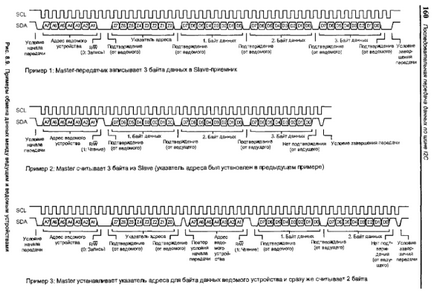

У процедурі читання зміни будуть трішки складніше, оскільки між зчитуванням байтів даних має бути підтвердження від ведучого, а після зчитування останнього байта підтвердження бути не повинно, далі йде умова завершення передачі (умова СТОП).

Про переривання ISR (TWI_INT) говорити нічого не буду, просто наведу приклад використання (зазвичай цього достатньо, відразу стає все зрозуміло):

Все, залишається створити проект в AVR STUDIO:

В налаштуваннях проекту вкажіть який-небудь MEGA (atmega16 наприклад), підключіть файли i2c_eeprom.c і i2c_eeprom.h.

У програмі я явно вказав частоту тактирования мого контролера 16 Mhz. Далі, в Proteus, ми виберемо якусь мікросхему зовнішньої пам'яті I2C EEPROM. Не забудьте після цього порівняти настройки в i2c_eeprom.h з параметрами обраної мікросхеми (slaveF_SCL. SlaveAddressConst - достовірну інформацію завжди можна дізнатися з даташітов).

Отже, залишається зібрати проект і переходимо до моделювання ..

III. Моделюємо роботу з I2C EEPROM в Proteus

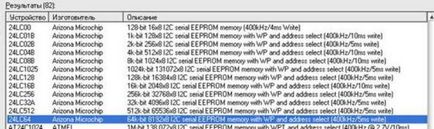

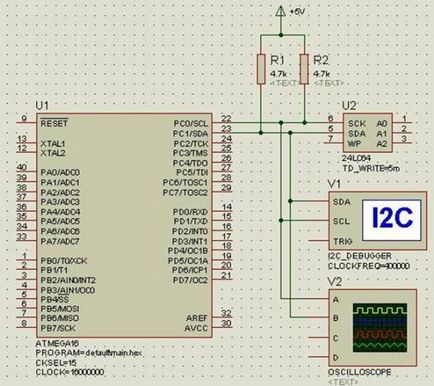

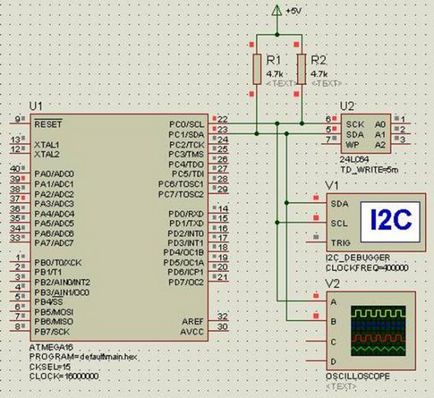

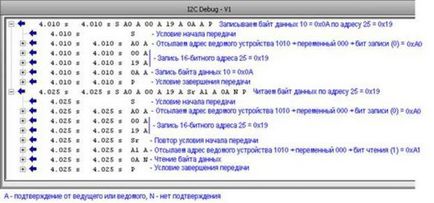

Додаємо на схему ATmega16, 2 резистора для підтяжки шини I2C (див. Схему на початку статті). З вкладки віртуальні інструменти візьміть Осциллограф і I2C-Отладчик. Для вибору пам'яті введіть в пошук I2CMEMS у вікні вибору пристроїв:

З усього списку я вибрав 24LC64 з об'ємом пам'яті 64 КБ і частотою роботи з шиною I2C 400 КГц.

В налаштуваннях контролера вкажіть прошивку, частоту тактирования 16 МГц і не забудьте виставити CKSEL-фьюз для кристала. В налаштуваннях I2C-відладчика вкажіть, що тактова частота імпульсів шини 400 КГц.

Тепер можна опуститися ще на рівень нижче і подивитися на осциллограмму:

[4] Microchip 24AA64 / 24LC64 datasheet

Щось я не те скопіпастіл.