JTAG (вимовляється «джей-таг»; скорочення від англ. Joint Test Action Group) - назва робочої групи з розробки стандарту IEEE 1149. Пізніше це скорочення стало міцно асоціюватися з розробленим ними спеціалізованим апаратним інтерфейсом на базі стандарту IEEE 1149.1. Офіційна назва стандарту Standard Test Access Port and Boundary-Scan Architecture. Інтерфейс призначений для підключення складних цифрових мікросхем або пристроїв рівня друкованої плати до стандартної апаратури тестування і налагодження.

На поточний момент інтерфейс став індустріальним стандартом. Практично всі скільки-небудь складні цифрові мікросхеми оснащуються цим інтерфейсом для:

· Вихідного контролю мікросхем при виробництві;

· Тестування зібраних друкованих плат;

· Прошивки мікросхем з пам'яттю;

· Налагоджувальних робіт при проектуванні апаратури і програмного забезпечення.

Метод тестування реалізований в стандарті отримав назву Boundary Scan (граничне сканування). Назва відображає первісну ідею процесу: в мікросхемі виділяються функціональні блоки, входи яких можна було від'єднати від решти схеми, подати задані комбінації сигналів і оцінити стан виходів блоку. Весь процес проводився виключно спеціальними командами по інтерфейсу JTAG, ніякого фізичного втручання не було потрібно. Був також розроблений стандартний мову управління цим процесом - Boundary Scan Description Language (BSDL).

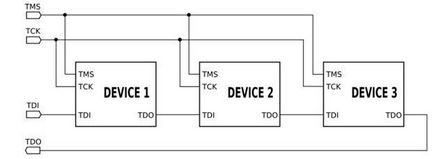

Стандарт передбачає можливість підключення великої кількості пристроїв (мікросхем) через один фізичний порт (роз'єм).

Порт тестування (TAP - Test Access Port) являє собою чотири або п'ять виділених висновків мікросхеми: ТСК, TMS, TDI, TDO і (опціонально) TRST.

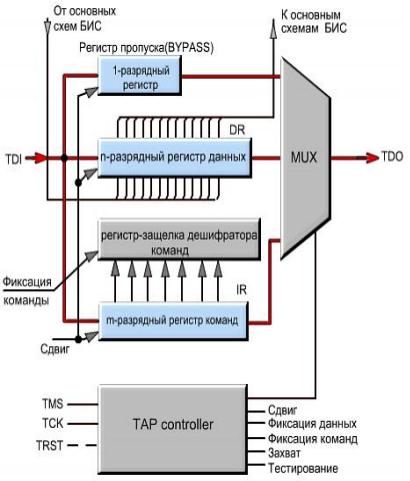

JTAG-порт мікросхеми та осередки периферійного сканування.

Функціональне призначення цих ліній:

TDI (test data input - «вхід тестових даних») - вхід послідовних даних периферійного сканування. Команди і дані вводяться в мікросхему з цього висновку по передньому фронту сигналу TCK;

TDO (test data output - «вихід тестових даних») - вихід послідовних даних. Команди дані виводяться з мікросхеми з цього висновку по задньому фронту сигналу TCK;

TCK (test clock - «тестове тактирование») - тактирует роботу вбудованого автомата управління периферійним скануванням. Максимальна частота сканування периферійних осередків залежить від використовуваної апаратної частини і на даний момент обмежена 25 ... 40 МГц [джерело не вказано 354 дня];

TMS (test mode select - «вибір режиму тестування») - забезпечує перехід схеми в / з режиму тестування і перемикання між різними режимами тестування.

Робота коштів забезпечення інтерфейсу JTAG підпорядковується сигналам автомата управління, вбудованого в мікросхему. Стану автомата визначаються сигналами TDI і TMS порту тестування. Певне поєднання сигналів TMS і TCK забезпечує введення команди для автомата і її виконання.

Схема управління JTAG інтерфейсом.

До складу схеми входять:

- Три зсувних регістра (реєстр команд (IR), регістр пропуску (Bypass) і регістр даних (DR);

- Вихідний мультиплексор (MUX);

- Контролер управління (TAP Controller).

Мал. 13.1. Устаткування JTAG інтерфейсу.

Основним регістром є регістр даних, він служить джерелом і приймачем даних при виконанні в JTAG ланцюжках будь-яких команд. З точки зору пристрої управління, регістр даних є одним з трьох зрушуютьсярегістрів, що включаються між контактом для подачі вхідної інформації (контакт TDI) і контактом для отримання вихідної інформації (контакт TDO).

Якщо на платі встановлено кілька пристроїв, що підтримують JTAG, вони можуть бути об'єднані в загальну ланцюжок. Унікальною особливістю JTAG є можливість програмування не тільки самого мікроконтролера (або ПЛІС), але і підключеної до його висновків мікросхеми флеш-пам'яті. Причому існує два способи програмування флеш-пам'яті з використанням JTAG: через завантажувач з подальшим обміном даними через пам'ять процесора, або через пряме управління висновками мікросхеми.

Мал. 13.2. підключення декількох мікросхем до одного інтерфейсу.

Програмне забезпечення роботи з цим інтерфейсом здійснюють Продукти JTAG Live. Сімейство програмних продуктів JTAG Live призначене насамперед для розробників, що займаються налагодженням нових або існуючих виробів. JTAG Live грунтується на периферійному скануванні - методі, що дозволяє точно локалізувати несправності в цифрових схемах. При цьому продукти JTAG Live не є професійними автоматичними системами; всі тести створюються вручну. Тому для роботи не потрібен net-лист. Ви просто вибираєте необхідні висновки мікросхем з підтримкою JTAG і перетаскуєте їх в робочу область. Після цього ви можете перевірити наявність контакту між зазначеними точками, короткого замикання або вважати логічне значення на тій чи іншій ланцюга. Таким чином, можна працювати навіть зі складками плат!

JTAG Live дозволяє вам використовувати кілька варіантів з'єднання модуля, що тестується з ПК. Дані кошти працюють зі стандартними USB-программаторами від Altera і Xilinx. Є також можливість підключити контролер JT3705 / USB від JTAG Technologies. Ви можете почати прямо сьогодні абсолютно безкоштовно. Завантажте базову версію JTAG Live і спокійно користуйтеся. За допомогою Buzz ви можете дуже швидко визначити до двох каналів периферійного сканування і відразу ж перевірити цілісність ланцюжка. Після перевірки інфраструктури, Buzz тут же дозволяє працювати з висновками компонентів.

Buzz також дає дуже зручну можливість перевірки наявності контакту між двома пинами, якщо вони з'єднані ланцюгом на перевіряється платі. При цьому програма видає всім знайомий звук, що імітує сигнал звичайного мультиметра. У вікні вимірювань ви можете вибрати висновок ІМС, де встановіть потрібний логічний рівень, і вважати рівень на будь-якому іншому виведення цього ж або іншого кристала.

Спробуйте перевірити наявність резистора підтяжки шляхом установки драйвера відповідного висновку в третій стан (High-Z). Buzz дозволяє також зняти показання на групі ланцюгів, якщо вони з'єднані між собою, що виходить за рамки можливостей звичайного мультиметра. Встановіть якесь значення на обраної ніжці мікросхеми і перевірте цей сигнал на всіх інших входах пристроїв на платі.

Якщо ви хочете просунутися далі простий «прозвонки» і зондування окремих ланцюгів, ви можете розглянути використання програм створення тестів JTAG Live Clip and Script. C їх допомогою можна зберігати тестові програми для їх використання у виробництві. Clip - це доповнення, що дозволяє вручну створювати необхідні векторні тести для певних кіл. Script добре поєднує периферійне сканування і функціональний тест за допомогою використання вбудованої мови програмування PythonTM. Однак зауважимо. що Live Clip і Script платнае програми.

Апаратна підтримка інтерфейсу - JT 3705 / USB.

Мал. 13.3. Зовнішній вигляд контролера JT 3705 / USB Explorer.

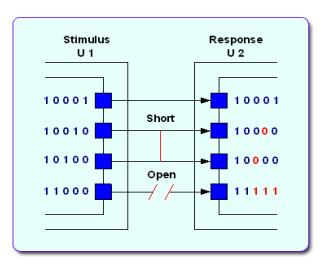

Тест зовнішніх з'єднань (Chip external connection test) з використанням JTAG

• Припустимо, що в схемі дві помилки:

• замикання між лініями 2 і 3, а також

• Припустимо, що замикання проявляється як wired-AND і розрив як

постійна наявність логічної 1.

Ріс.13.4. Тестування з'єднань.

Огляд оpensource JTAG інструментів.

ldoolitt / jtag.html) перша спроба розробки програмного шару для доступу з хоста (for host-side access) до JTAG Test Access Ports. Більшість розробників розробляють свої дублюють один одного рішення, особеннос коли намагаються домогтися переносимості між JTAG адаптерами, реалізують отладчики, або реалізують автодетект пристроїв в JTAG ланцюжку. Спроба ком'юніті розробити уніфікований компонент для виконання цих завдань на основі загального API для mid-level доступу до JTAG пристроїв. Це дозво розробникам високорівневих додатків не вигадувати колесо працюючи з низькорівневими деталямт такими як JTAG pins, etc.