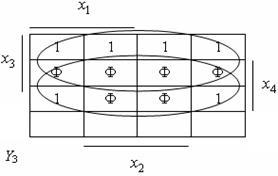

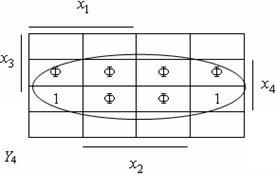

Мал. 4.1. Карти Карно перетворювача кодів

Схема, виконана на підставі цих структурних формул в базисі І-НЕ, наведена на рис. 4.2.

Мал. 4.2. Структурна схема перетворювача кодів

Шифратори - перетворювачі позиційного коду в двійковий, т. Е. Що перетворюють сигнал 1 на одному з входів до відповідного код на вихідних шинах. Якщо на виході знімається m - розрядний код, то максимальне число входів n = 2 m. Якщо використовуються всі 2 m входи, то такий шифратор називають повним, якщо не все, - то неповним. Функціонування шифратора 4 2 представлено таблицею істинності (табл. 4.2). З таблиці випливає:

т. е. для побудови такого шифратора потрібно два ЛЕ АБО на два входи.

Аналогічно будуються шифратори на більше число розрядів.

Недолік таких шифраторів - неоднозначність, якщо порушено одразу кілька входів. Щоб шифратор відгукувався тільки на один збуджений вхід, будують пріоритетні шифратори. У них, в разі одночасного збудження декількох входів, вихідний код буде відповідати «старшому» ( «молодшому») номеру з порушених входів. На рис. 4.3 наведено позначення такого шифратора. Пріоритетний шифратор має додаткові висновки: Е1 - сигнал включення шифратора, Е0 - сигнал про відсутність порушених входів, G - сигнал на виході, який свідчить про наявність хоча б одного порушеної входу.

Наявність висновків Е1. Е0, G дозволяє нарощувати розрядність шифраторів.

Дешифратор - перетворювач двійкового n- розрядного коду в унітарний 2 n-розрядний код, т. Е. Дешифратор має n входів і m = 2 n виходів. Кожному набору вхідних змінних відповідає збудження (поява логічної одиниці або нуля) на виході, десятковий номер якого відповідає бінарного коду.

Розглянемо приклад побудови двухразрядного дешифратора. Функціонування дешифратора можна уявити таблицею істинності (табл. 4.3) З таблиці отримаємо вирази для функцій виходу (Y1) дешифратора:

З отриманих співвідношень видно, що для побудови дешифратора потрібно чотири логічних елемента І на два входи і два інвертора. Часто дешифратори будуються в базисі І-НЕ (див. Рис. 4.4). В цьому випадку виходи будуть інверсними, т. Е. Порушеній виходу відповідає логічний нуль; і щоб отримати прямий вихід, треба ще чотири інвертора. Для розширення можливостей дешифратора в інтегральних схемах робиться ще один вхід Е - дозвіл. Для його організації беруться елементи І-НЕ на 3 входи - треті входи об'єднаються і утворюють вхід дозволу. В цьому випадку дешифратор працює, коли на вході Е логічна одиниця.

Мал. 4.4. структура дешифратора

Графічне зображення дешифраторів наведено на рис. 4.5. Якщо виходи інверсні, то позначаються кружечками.

Наявність входу дозволу дозволяє нарощувати розрядність дешифратора. На рис. 4.6 показано, як побудувати трьохрозрядний дешифратор, використовуючи двухразрядного.

Мал. 4.6. нарощування дешифраторів

Для всіх наборів вхідних змінних, де x3 = 0, буде працювати DC 2, т. К. На його вхід Е2 буде приходити одиниця. Коли x3 = 1, відповідно працює дешифратор DC 3. Таким чином, виходить три входи і вісім виходів. Для розширення числа входів і виходів можна скористатися паралельним (прямокутним) дешифратором, але для цього, крім дешифраторів, потрібні елементи 2И.

Використовуючи дешифратори і додаткові логічні елементи, можна реалізувати практично будь-яку логічну функцію.

Розглянемо такий приклад

Таблиця істинності для цієї функції має вигляд табл. 4.4. Для її реалізації необхідний дешифратор 2 4 і логічний елемент АБО на два входи (рис. 4.7). Коли x1 або x2 рівні одиниці (для набору n = 1 і n = 2), на виходах дешифратора (1 або 2) з'являється одиниця і відповідно вихідна функція буде дорівнює 1.

Мал. 4.7. Структурна схема суматора

по модулю 2 на дешифраторі

Функціонування двухразрядного мультиплексора представлено таблицею істинності (табл. 4.5). Робота мультиплексора описується логічним рівнянням

Відповідно до рівняння для побудови мультиплексора необхідний елемент 3І-4ІЛІ і два інвертора. Структурна схема приведена на рис. 4.8, графічне зображення мультиплексорів - на рис. 4.9.

Мал. 4.7. Структурна схема мультиплексора

Мал. 4.9 Умовне позначення мультиплексорів

Мал. 4.10. Схема нарощування мультиплексорів

Мал. 4.12. умовне зображення

демультиплексор

Треба зауважити, що мультиплексори і демультиплексори в серіях на біполярних транзисторах коммутируют тільки цифрові сигнали, т. Е. 0 або 1.

Мал. 4.12. Функціональна схема мультиплексора-демультиплексор

Сумматором називається комбінаційна схема, призначена для додавання двійкових чисел. Найпростіша задача - складання двох однорозрядних чисел. Для того щоб розробити логічну схему, в першу чергу слід розглянути всі можливі поєднання вхідних змінних, на підставі чого можна скласти таблицю станів. При додаванні однорозрядних чисел A і B можуть спостерігатися такі комбінації:

т. е. якщо A = B = 1, відбувається перенесення в наступний (більш старший) розряд. Отже, такий акумулятор повинен мати два виходи: один для формування частини суми, що відноситься до даного розряду, і другий - для перенесення в наступний розряд. Представляючи числа і логічними змінними a0. b0. складемо таблицю станів (табл. 4.8), де S0 - сума, P - сигнал перенесення.

Звідси складаємо логічні рівняння в СДНФ:

і будуємо структурні схеми (рис. 4.14, рис. 4.15).

Мал. 4.14. Суматор за модулем два Рис. 4.15. схема перенесення

Схема, що реалізує рівняння 1, називається виключає АБО, випускається в серіях як окрема мікросхема. Графічне позначення наведено на рис 4.16. Логічна операція, яка виконується цією схемою, -

де - символ підсумовування по модулю два.