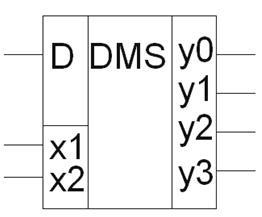

Принципова схема муль-тіплексора показана на рис. 25, б.

У тих випадках, коли потрібно передавати на виходи багато-розрядні вхідні дані в паралельній формі, використовується паралельне включення мультиплексорів по числу розрядів пе-редавать даних.

y0 = x1 * x2 * D, y2 = x1 * x2 * D,

y0 = x1 * x2 * D, y0 = x1 * x2 * D.

Використання демультиплексор може істотно спрощено-стить побудова логічного пристрою, що має кілька ви-ходів, на яких формуються різні логічні функції од-них і тих же змінних.

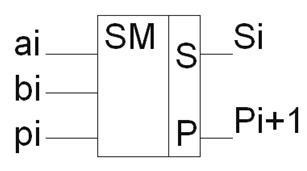

Однорозрядного двійкового суматора.

З розглянутого раніше принципу складання багаторозрядних двійкових чисел слід, що в кожному з розрядів виробляються однотипні дії: визначається цифра суми шляхом додавання за модулем 2 цифр доданків і надходить в даний розряд переносу і формується перенос, який передається в наступний розряд. Ці дії реалізують-ся однорозрядним двійковим сум-Матора. Символічне зображені ження такого суматора показано на рис. 27, а. Він має три входи для подачі цифр розрядів складаючи-ваних ai. bi і перенесення рi; на ви-ходах формуються сума si. і перенесення pi + 1, i призначений для передачі в наступний розряд.

У однорозрядного сумматоре можуть передбачатися входи для подачі як прямих значень розрядів доданків ai. bi і перенесення рi, так і інверсних значень, а також виходи, на яких формуються інверсні значення вихідних змінних.

У таблиці 6 показаний закон функціонування однорозрядного суматора.

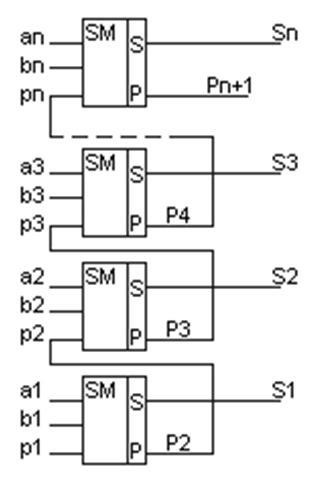

Багаторозрядні двійкового суматора.

Залежно від способу введення розрядів доданків суматори поділяються на два типи: послідовного і паралельного дії. У суматори першого типу розряди чисел вводяться в послідовник-ний формі, т. Е. Розряд за розрядом (молодшим розрядом вперед), в суматори другого типу кожне з доданків подається в парал-інтер- формі, т. Е. Одночасно всіма розрядами.

Суматор послідовної дії. Складається з одноразряд-ного

суматора, вихід pi + 1 якого з'єднаний з входом pi через елемент затримки, параметри якого узгоджені зі швидкістю надходження розрядів доданків на входи суматора. Операція підсумовування у всіх розрядах доданків здійс-ствляется за допомогою одного і того ж однорозрядного суматора, але послідовно в часі, починаючи з молодших розрядів. Таке по-будова сумматора можливо за рахунок того, що складові надходять в після-послідовно формі.

Очевидна гідність суматора послідовної дії полягає в малому обсязі обладнання, необхідного для його побудови. Однак пов'язаний-ва з цим необхідність в послідовній обробці розрядів призводить до вкрай низького швидкодії. Тому. суматори такого типу в даний час використовуються дуже рідко.

Суматор паралельної дії. Складається з окремих раз-рядів, кожен з яких містить однорозрядних суматор (рис. 28).

При подачі доданків цифри їх розрядів надходять на відповід-ветствующие однорозрядні суматори. Кожен з одноразряд-них сумматоров формує на своїх виходах цифру відповідаю-ного розряду суми і перенесення, який передається на вхід одноразряд-ного сумматора наступного (більш старшого) розряду.

Така організація процесу організації перенесення, звана послідовним переносом, знижує швидкодію багаторозрядних суматорів, тому що отримання результату в старшому розряді суматора забезпечується тільки після завершення поширення перенесення в усіх розрядах.

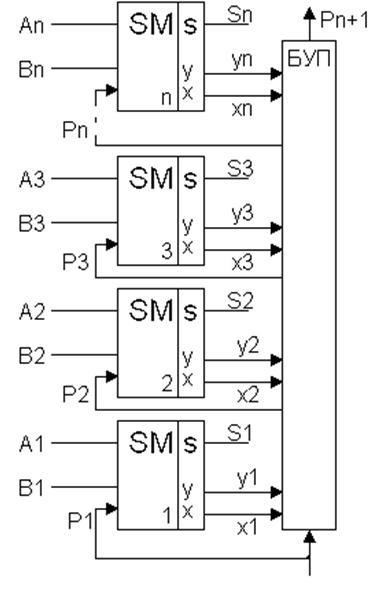

Підвищення швидкодії паралельних суматорів. Для забезпечення високої швидкодії паралельні суматори повинні будуватися на елементах, що володіють високим бистродей-наслідком.

У найбільш несприятливому випадку виник в млад-шем розряді перенесення може послідовно викликати переноси у всіх інших розрядах. При цьому час передачі приносив t = t1 * n, де t1 -затримка поширення перенесення в одному раз-ряді.

Зменшення t досягається наступними прийомами.

1. При побудові схем однорозрядних суматорів прагнуть до зменшення числа елементів у ланцюзі між входом, на який надходить імпульс перенесення рi і .виходом, на якому формує-ся передається в наступний розряд імпульс перенесення pi + i.

2. У ланцюгах від pi до pi + 1 застосовують елементи з підвищеною швидкодією.

3. Схеми сумматоров слід будувати таким чином, щоб сигнали з виходу кожного логічного елемента в ланцюзі від рi. до pi + i надходили на якомога меншу кількість інших логічних елементів, оскільки приєднання кожного додаткового еле-мента до тій чи іншій точці ланцюга переносів, як правило, призводить до збільшення паразитної ємності, подовженню фронтів сигналів і, отже, до збільшення затримки поширення сигналу і зниження швидкодії суматора.

4. Застосовують пристрою формування переносів в парал-інтер- формі. У показаному на рис. 29 сумматоре за допомогою пристрою, званого блоком прискореного перенесення, вироб-диться формування переносів в паралельній формі, т. Е. Одне-тимчасово для всіх розрядів. Перенесення з цього блоку надходять в усі розрядні суматори одночасно. При цьому розрядні суматори не містять ланцюгів формування переносів, вони фор-міруют тільки суму Si і величини Yi і Xi, для отримання кото-яких переноси не потрібні. Ці величини Yi і Xi необхідні для формування переносів в блоці прискореного перенесення, вони визна-ділячи наступні ситуації: Yi = 1 означає, що в i-му розряді пе-ренос pi + 1 в наступний (p + 1) -й розряд необхідно формувати незалежно від надходження в даний розряд перенесення з попе-ного розряду; Xi = 1 означає, що в i-му розряді перенесення рi + i дол-дружин формуватися тільки за умови надходження перенесення рi. з попереднього розряду:

Yi = a1 * b1; X1 = (a1 + b1) * p1.

Величини Yi і Xi формуються одночасно у всіх розрядних суматорах, одночасно по-ступають на входи блоку прискореного перенесення і, отже, в цьому блоці одночасно формуються переноси, що подаються в розрядні суматори. Після надходження переносів з блоку ус-корінного перенесення в розрядних суматорах формуються суми Si.

Так як логічні елементи, що входять до складу КЦУ, переключаються з затримкою tзад. то при зміні в не-який момент часу комбінації вхідних сигналів вихідні сигнали пристрою (якщо вони змінюються в ре-док цього) візьмуть встановилися значення тільки після того, як закінчаться перехідні процеси в соот-відних логічних елементах. На шляху від входів пристрою до його виходів окремі логічні елементів-ти включені послідовно. Тому тривалість пе-реходних процесів буде залежати від числа логічних елементів, які включені в такому ланцюжку. Примі-няемое в даний час методика визначення tзад в логічних елементах, що передбачає вико-вання при вимірюванні ланцюжка включених один за одним однотипних логічних елементів, дозволяє при оцінці загальної затримки в такому ланцюжку підсумувати затримки окремих логічних елементів. При оцінці бистродей-наслідком КЦУ необхідно виявити ту ланцюжок логічних елементів між входами і виходами пристрою, кото-раю буде задавати найбільшу затримку, і скласти між собою затримки логічних елементів цієї цепоч-ки. Зазвичай вона містить найбільшу кількість включених один за одним від входів до виходів логічних елементів-тов. Але можуть бути виключення, пов'язані, наприклад, з наявністю в коротшою ланцюжку окремих інерції-ційних логічних елементів з великим tзад. Тому в загальному випадку необхідно проаналізувати всі цепоч-ки логічних елементів від входів до виходів і виявити таку, яка дає найбільшу затримку.

ЗМАГАННЯ В КЦУ.

Неоднакову затримку проходження сигналу в від-ділових частинах КЦУ іноді асоціюють з «змагання-ми» в швидкості перемикання логічних елементів. В результаті цього явища на виходах деяких еле-ментів можуть з'являтися імпульсні перешкоди. У деяких випадках неоднакова затримка перехожих-дення сигналу в окремих ланцюжках логічних елементів-тов може привести до імпульсної заваді і на виході КЦУ. Покажемо це на прикладі.

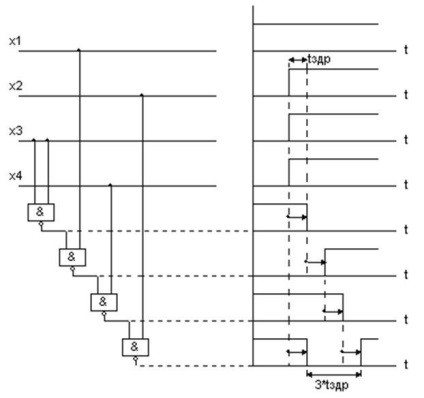

Розглянемо КЦУ представлену на рис. 30, а. Вхідний сигнал змінюється з коду 1000 Перейти код 1111. Затримка в кожному логічному елементі tзад. Структурна схема КЦУ і тимчасові діаграми для даного прикладу наведені на рис. 30, б. В даному випадку на виході КЦУ при зміні коду вхідного сиг-налу 1000 Перейти код +1111 короткочасно встановлюється нульове значення (на час 3 * tздр), хоча за умовами роботи вихідне значення мало зберегтися на одиничному рівні.

Це безпосередньо випливає з тимчасових діаграм, якщо знехтувати затримками перемикання логічних елементів Коли тривалість перешкоди перевищить певну величину, можливо на-рушення працездатності підключених до виходу КЦУ пристроїв (тригерів, лічильників і т. Д.). У подібних випадках «змагання» називають «небезпечними».

Для боротьби з «небезпечними змаганнями» мож-но прийняти різні заходи. По-перше, іноді можна предусмот реть такий порядок зміни вхідних кодів, при якому або імпульсні перешкоди не будуть з'являтися на виході взагалі, або їх тривалість зменшиться до безпечної величини. В необхідних випадках таку затримку можна ввести штучно включенням ланцюжка з парного числа інверторів. По-друге, при синтезі відповідного КЦУ можна іноді знайти такий варіант структурної формули (а слідчий-но, і структурної схеми), при якому вдається зменшити величину імпульсної перешкоди.

У подібних випадках «змагання» називають «небезпечними». Для боротьби з «небезпечними змаганнями» мож-но прийняти різні заходи. По-перше, іноді можна предусмот реть такий порядок зміни вхідних кодів, при якому або імпульсні перешкоди не будуть з'являтися на виході взагалі, або їх тривалість зменшиться до безпечної величини. В необхідних випадках таку затримку можна ввести штучно включенням ланцюжка з парного числа інверторів. По-друге, при синтезі відповідного КЦУ можна іноді знайти такий варіант структурної формули (а слідчий-но, і структурної схеми), при якому вдається зменшити величину імпульсної перешкоди.

По-третє, можна організувати синхронну передачу сигналів від одного пристрою до іншого. Для цього вводяться спеціальні імпульси синхронізації, які задають моменти передачі інфор-мації між окремими пристроями. Пауза між імпульсами синхронізації може бути обрана такою, щоб за її час закон-чілісь перехідні процеси і на виходах пристроїв встановилися стаціонарні значення.

Синхронна передача інформації в сучасних цифрових пристроях застосовується дуже широко. Це питання вже обговорював-ся раніше, наприклад при розгляді типових КЦУ, в тому числі мультиплексорів. Відзначимо, що наявність «змагань» і возникаю-щие при цьому імпульсні перешкоди впливають на надійність цифрових пристроїв.