З чого складається продуктивність процесора? Раніше в ходу була формула, що описує швидкодію як добуток кількості виконуваних за один такт інструкцій і частоти, на якій цей процесор функціонує. Тепер в цій формулі з'явився і третій співмножник - кількість обчислювальних ядер. Тому розробник процесорів, який бажає випустити швидкий продукт, має для цього кілька шляхів.

Однак не все так просто. Збільшення кількості виконуваних обчислювальним ядром за такт інструкцій - досить складне завдання. Класичний x86 програмний код передбачає послідовне виконання команд, а тому, щоб домогтися їх паралельної обробки, в процесор необхідно закласти високоефективні блоки передбачення переходів і переупорядочивания інструкцій, реалізація яких вимагає чималих інженерних зусиль. При цьому ускладнення мікроархітектури позначається на фізичних розмірах кристала і призводить до обмежень при нарощуванні кількості ядер. Так що якщо виробник збирається зробити процесор з великим числом ядер, то микроархитектуру потрібно, навпаки, намагатися спростити. Непросто все і з тактовою частотою. Ставка на її зростання знову зажадає внесення змін у внутрішні блоки процесора і подовження його виконавчого конвеєра. У підсумку виходить наступне: щоб процесор міг завоювати медальку за продуктивність, його розробники повинні неабияк попітніти над одночасною оптимізацією цілого ряду параметрів.

Проблема полягає ще і в тому, що будь-який з обраних шляхів поліпшення швидкодії процесора може виявитися вдалим лише для окремих випадків. Далеко не всі програми можуть ефективно працювати з великою кількістю ядер. Якісь алгоритми не дозволяють коректно прогнозувати переходи і змінювати порядок інструкції. А в деяких випадках продуктивність не росте і зі збільшенням тактової частоти, тому що в системі знаходяться якісь інші вузькі місця.

Підібрати оптимальний баланс непросто, та й що вважати критерієм оптимальності? Ми можемо лише зіставити продуктивність процесорів в кінцевому числі програм і вибрати з них найшвидший для даного конкретного випадку. Однак це зовсім не гарантує, що, застосувавши інший набір тестового інструментарію, ми не отримаємо абсолютно протилежні оцінки. Настільки великий вступ наведено тут тому, що сьогодні ми маємо знайомство з новою серією процесорів AMD FX - флагманським продуктом компанії AMD, широко відомим під кодовим ім'ям Zambezi. В основі цього процесора лежить вельми неоднозначна мікроархітектура Bulldozer, яка вже встигла зібрати чималий букет невтішних відгуків. Але справа зовсім не в тому, що ця мікроархітектура зовсім погана. Підбираючи найкращий баланс характеристик, розробники невірно оцінили потреби більшості користувачів і зробили в «базову формулу» основний акцент не на той співмножник. У підсумку початковий задум з випуску високопродуктивного рішення нового покоління пішов шкереберть і зацікавлені обіцянками прориву прихильники AMD отримали зовсім не те, що очікували. Однак чи є це серйозним і об'єктивним приводом для розчарування? Про це і поговоримо в даному матеріалі.

# 8673; # Вважаємо ядра: вісім або чотири?

Працюючи над новим дизайном для продуктивних процесорів, AMD вирішила поставити на чільне місце кількість обчислювальних ядер. Це цілком логічний вибір, заснований на тому, що з роками многопоточного програмного забезпечення стає все більше і більше і розробка мікроархітектури, розрахованої на багаторічне розвиток, повинна враховувати в першу чергу не поточний стан ринку, а спостережувані тенденції. Вісім ядер, передбачених в базовому варіанті нового процесора, - це те, чим AMD і збиралася підкорити ринок, на якому поки що були представлені тільки чіпи, максимальна кількість ядер в яких обмежувалося шістьма. (Тут ми говоримо тільки про настільних комп'ютерах. - прим. Ред.)

При цьому брати ядра старої мікроархітектури K10 розробники не захотіли. Вони не тільки мають занадто великий фізичний розмір, а й, як можна судити по Llano, не схильні до функціонування на високих тактових частотах навіть після перекладу на сучасну 32-нм технологію. До того ж вони не підтримують багатьох сучасних можливостей, таких як, наприклад, AVX-інструкції. Тому, для збірки восьміядерніков AMD зробила нову мікроархітектуру - Bulldozer. Представники компанії вважають за краще говорити, що її розробка велася з чистого аркуша, але насправді ж в ядрах Bulldozer можна знайти чимало відсилань до іншої представленої в цьому році мікроархітектурі - Bobcat, орієнтованої на застосування в компактних і енергоефективних пристроях. Втім, спорідненість між Bulldozer і Bobcat - досить віддалене, і згадуємо ми про нього лише для того, щоб стала зрозуміла загальна ідея - в Bulldozer об'єднано багато порівняно нескладних ядер.

При цьому мова йде зовсім про примітивне суміщенні на одному напівпровідниковому кристалі восьми простих ядер. При такому розкладі вийшов процесор мав би зовсім невисокою однопоточному продуктивністю, і це стало б досить серйозною проблемою, так як програм, які не дроблять навантаження на кілька обчислювальних потоків, не так вже й мало. Тому, по-перше, ядра були оптимізовані під роботу на високих тактових частотах. А по-друге, вони були спарені в двоядерні модулі, здатні спільно використовувати свої ресурси на благо обслуговування одного потоку. В результаті вийшла досить цікава конструкція: вхідна частина виконавчого конвеєра у такого двоядерного модуля - загальна, а в подальшому обробка інструкцій ділиться між двома наборами виконавчих пристроїв.

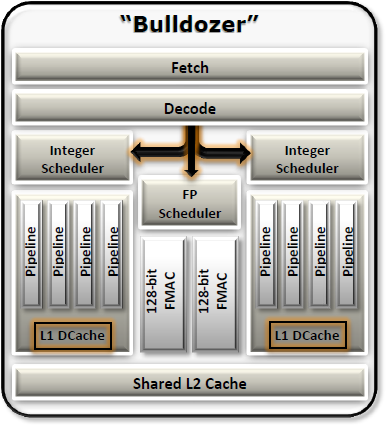

Основа конструкції Bulldozer - умовно званий двоядерним модуль

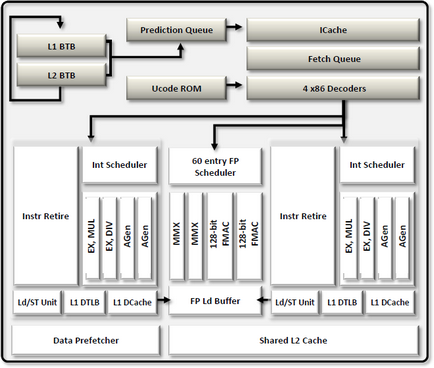

Нагадаємо, процес обробки даних в сучасному процесорі включає кілька етапів: вибірку x86-інструкцій з кеш-пам'яті, їх декодування - переклад у внутрішні макрооперації, виконання, запис результатів. Перші два етапи в модулі Bulldozer виробляються для пари ядер спільно, а далі для цілочисельних інструкцій виконання розподіляється по двом ядрам-кластерам або, в разі дійсної арифметики, воно здійснюється в загальному для двох ядер блоці операцій з плаваючою крапкою.

Модулі Bulldozer розраховані на обробку чотирьох інструкцій за такт, причому, завдяки технології макросліянія, деякі пари x86-інструкцій можуть розглядатися процесором як одна операція. Це означає, що в цілому двоядерний модуль Bulldozer за своєю потужністю подібний одному ядру сучасних интеловских процесорів, які також можуть обробляти по чотири інструкції за такт і при цьому теж підтримують макросліянія.

Так виглядає функціональний пристрій модуля, побудованого на мікроархітектурі Bulldozer. Від двох ядер залишилося лише два набори цілочисельних виконавчих пристроїв

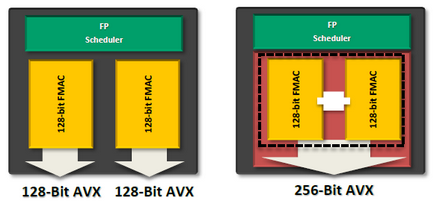

Відносно невисоку складність має і загальний на процесорний модуль блок операцій з плаваючою крапкою. У нього входить два 128-бітних виконавчих пристрої FMAC, які для обробки 256-бітних інструкцій можуть об'єднуватися в єдине ціле. Здавалося б, і тут виконавчих пристроїв не так багато, особливо з урахуванням того, що діляться вони на пару ядер. Але зате вони - більш універсальні, ніж в попередніх і конкуруючих мікроархітектури, де застосовуються окремі умножители і суматори. І завдяки цьому в певних випадках при роботі з числами двоядерний модуль Bulldozer може забезпечувати порівнянну і навіть більш високу продуктивність, ніж, наприклад, одне ядро Sandy Bridge.

Аналогічна ідея об'єднання 128-бітних пристроїв для роботи з 256-бітними інструкціями використовується і в Sandy Bridge

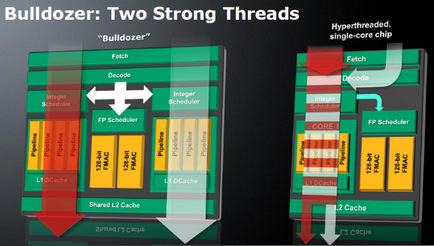

Однак свої найсильніші сторони модуль Bulldozer повинен проявляти при двухпоточной навантаженні. Одне ядро Sandy Bridge теж здатне обробляти два обчислювальних потоку, для цього в ньому є технологія Hyper-Threading. Однак все інструкції при цьому направляються на один набір виконавчих пристроїв, що на практиці викликає численні колізії. У модулі Bulldozer ж збережено два незалежних цілочисельних кластера, які можуть виконувати потоки паралельно, а сумарна кількість виконавчих пристроїв в них перевищує число таких пристроїв в ядрі Sandy Bridge в півтора рази.

Зліва - модуль Bulldozer, праворуч - якесь конкуруюче ядро з підтримкою Hyper-Threading. Насправді на Sandy Bridge воно не дуже-то і схоже, але суть проблеми ілюстрація передає

В результаті модуль Bulldozer володіє вищою піковою продуктивністю, ніж ядро Sandy Bridge, але розкрити цю продуктивність трохи складніше. Ядро Sandy Bridge інтелектуально завантажує власні ресурси завдяки просунутої внутріпроцессорной логіці, самостійно розбиратися однопотоковий код і виконує його паралельно на повному наборі своїх виконавчих пристроїв. У Bulldozer ж завдання ефективного використання виконавчих пристроїв частково перекладається на програміста, який повинен розбити свій код на два потоки - повноцінна завантаження всіх потужностей модуля стане можливою лише тоді.

І ось що характерно. Розглядаючи двоядерний модуль процесора Bulldozer, ми весь час порівнювали його з одним ядром Sandy Bridge, і при цьому нам вдавалося проводити цілком коректні паралелі. Це змушує замислитися - чи не варто вважати «восьмиядерна» нової мікроархітектури породженням фантазії маркетологів? AMD говорить, що вважати ядра слід за кількістю цілочисельних кластерів, аргументуючи це тим, що модуль здатний забезпечити до 80% продуктивності двох незалежних ядер. Однак не слід забувати, що ядра, покладені в основу Bulldozer, істотно простіше ядер інших процесорів. Тому кількість двоядерних модулів - характеристика, що відображає продуктивність Bulldozer куди адекватніше.

Знайди максимальну кількість процесорних ядер і отримай роботу в маркетинговому відділі AMD

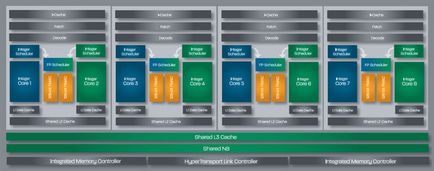

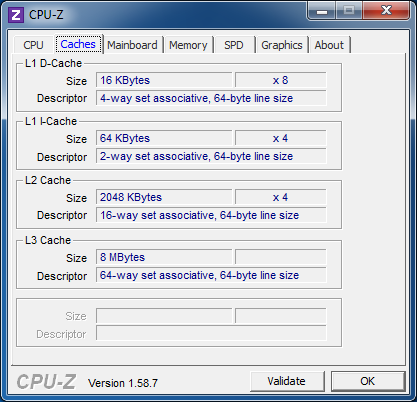

# 8673; # Кеш-пам'ять

Організація кеш-пам'яті в процесорах Bulldozer також «прив'язана» не стільки до окремим ядер, скільки до двоядерним модулів. Фактично на кожне ядро виділено лише власний кеш даних першого рівня, всі інші рівні кеш-пам'яті відносяться або до модуля в цілому, або до процесора:

- Кожне ядро має власну кеш-пам'ять першого рівня для даних. Її обсяг становить 16 Кбайт, а архітектура передбачає наявність чотирьох каналів асоціативності. Цей кеш працює за алгоритмом з наскрізною записом, що означає його інклюзивність.

- Кеш першого рівня для інструкцій представлений в єдиному екземплярі на кожен двопроцесорний модуль. Його обсяг - 64 Кбайт, а кількість каналів асоціативності - два.

- Кеш другого рівня також реалізується в одиничному на модуль екземплярі. Його розмір - значні 2 Мбайт, асоціативність - 16 канальна, а алгоритм роботи - ексклюзивний.

- Крім того, восьміядерний процесор в цілому має у своєму розпорядженні 8-мегабайтним L3 кешем з 64-канальної асоціативністю. Особливість цього кеша складається в його роботі на істотно меншою в порівнянні з самим процесором частоті, яка складає близько 2 ГГц.

Наступна таблиця описує співвідношення обсягів кеш-пам'яті процесорів восьмиядерних Bulldozer, чотирьохядерним Sandy Bridge і Thuban (шестиядерних Phenom II X6, побудованих на мікроархітектурі K10).

Згода на обробку персональних даних