Дякую вам за підтримку!

Сучасний стан напівпровідникових технологій Intel: 90-нм технологічний процес

Перш за все зупинимося на поточний стан справ корпорації в області напівпровідникових і мікропроцесорних технологій, оскільки новий 65-нм технологічний процес багато в чому є розвитком ідей, закладених в реалізації нинішнього покоління 90-нм мікропроцесорів. Отже, перерахуємо ключові моменти сучасної 90-нм технології.

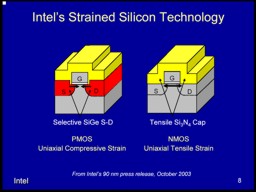

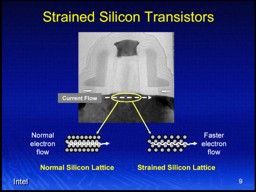

1. Технологія напруженого кремнію

Мабуть, на сьогоднішній день це найбільш відома «в масах» технологія, що відрізняє 90-нм технологічний процес Intel від попередніх. Вона спрямована на вирішення однієї з найважливіших завдань мікропроцесорної індустрії # 151; збільшення швидкості роботи транзисторів, що утворюють ядро процесора. Її принцип полягає в розтягуванні (в разі транзисторів NMOS) або стисненні (для транзисторів PMOS) правильної кристалічної решітки кремнію # 151; матеріалу каналу польового транзистора, що призводить до збільшення електронно-доречний провідності, тобто прискоренню проходження електричного струму через канал за рахунок зниження його опору (до 30% на PMOS-транзисторах і до 10% на NMOS-транзисторах). У свою чергу, за рахунок цього збільшується швидкість перемикання транзисторів, що виражається в кінцевому вигляді можливістю збільшення тактової частоти процесора (враховуючи, що ядро мікропроцесора є CMOS-рішення, тобто поєднання PMOS і NMOS-транзисторів, в середньому слід очікувати до 20% її збільшення). Стиснення або розтягнення правильної структури кристалічної решітки кремнію в загальному випадку є її «напругою», що і відбилося в назві даної технології.

Технологія напруженого кремнію Intel. зліва # 151; стисла кристалічна решітка кремнію PMOS-транзисторів і розтягнута кристалічна решітка кремнію NMOS-транзисторів; справа # 151; Протягом струму через правильну і напружену кристалічну решітку кремнію.

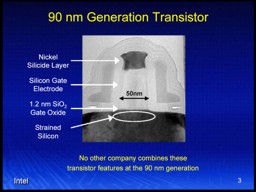

2. Удосконалені транзистори

Суттєвою складовою 90-нм технологічного процесу Intel є використання мініатюрних, високопродуктивних транзисторів, що володіють низьким енергоспоживанням і працюють при зменшеному напрузі (

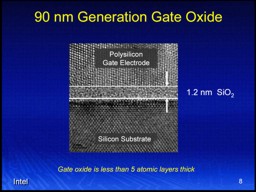

1.2 В). Транзистори характеризуються 50-нм завтовшки затвора, що виготовляється з полікристалічного кремнію із застосуванням покриття з силіциду нікелю (NiSi) # 151; матеріалу, що володіє більш низьким лінійним електричним опором у порівнянні з використовуваним раніше дисилицида кобальту (CoSi2) в областях довжин затвора менше 100 нм. Товщина діелектричного оксидного шару затвора в 90-нм транзисторах становить 1.2 нм, останній виготовляється зі звичайного діоксиду кремнію (SiO2), який добре зарекомендував себе на протязі останніх 30 років в якості матеріалу для даного компонента транзисторів, перш за все, внаслідок простоти його виготовлення (оксидний шар виготовляється прямо «на місці», тобто в процесі виробництва транзисторів, за допомогою термічного окислення поверхні підкладки). Крім цього, застосування даного матеріалу надає можливість подальшого збільшення швидкості роботи транзисторів за допомогою скорочення товщини утвореного їм ізолюючого шару (зрозуміло, лише до певної межі, про що піде мова нижче).

90-нм транзистори. зліва # 151; загальний вигляд транзисторів; справа # 151; оксидний шар затвора.

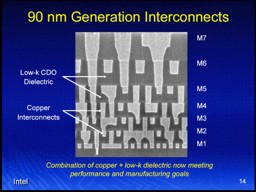

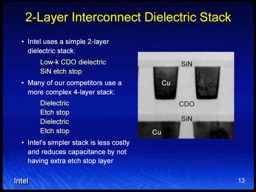

3. 7-шарові межтранзісторние з'єднання

Нинішній технологічний процес включає в себе використання 7-шарових мідних з'єднань високої щільності, що приводить до зниження загальної вартості продукції, а також нового типу діелектрика з низькою діелектричної константою (low-k), що представляє собою нітрид кремнію (SiN) в поєднанні з оксидним матеріалом ( точний склад якого не розкривається), допированного вуглецем (carbon-doped oxide, CDO). Це дозволяє знизити «міжконтактного» ємність на 18-20% в порівнянні з застосовуваним в 130-нм техпроцесу оксифторида кремнію (SiOF), що прискорює «внутрічіповую» комунікацію і знижує споживану чипом потужність.

90-нм межтранзісторние з'єднання. зліва # 151; загальний вид з'єднань; справа # 151; будова діелектричної прошарку.

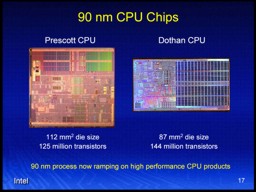

4. 300-мм виробничі підкладки

Мікропроцесорні ядра, що випускаються по 90-нм технологічному процесу.

Найближче майбутнє напівпровідникових технологій Intel: 65-нм технологічний процес

1. Удосконалена технологія напруженого кремнію

Технологія напруженого кремнію, що застосовується Intel починаючи з розглянутого вище 90-нм технологічного процесу, в 65-нм техпроцесу отримує свій подальший розвиток. За рахунок застосування більш сильною технології «напруги» кремнієвого каналу, в новому технологічному процесі досягається подальше збільшення швидкості перемикання транзисторів за рахунок зростання струму активності (ID. Або ION) на 10-15% при збереженні практично на постійному рівні струму витоку через оксидний шар затвора (IGate). Загальний виграш по тактовій частоті в результаті застосування поліпшеної технології напруженого кремнію другого покоління, згідно Intel, складе величину порядку 30% (в порівнянні з «ненапруженим» кремнієм).

2. Нові 65-нм транзистори

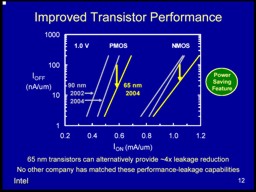

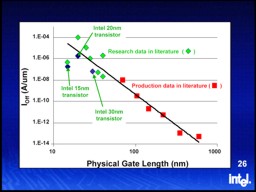

Транзистори, що виготовляються по 65-нм технологічному процесу, характеризуються подальшим зменшенням довжини нікель-сіліцідірованного полікремнієвих затвора до 35 нм при одночасному збереженні товщини оксидного шару затвора на рівні 1.2 нм. Остання обставина є причиною збереження струму витоку на колишньому рівні, а комбінація цих фактів зменшує ємність затвора (CGate) до 20%, що веде до зниження споживаної чіпом «активної» потужності. Проте, не слід забувати про таку важливу характеристику польового транзистора, як струм спокою (IOFF) # 151; струм, що проходить від джерела до стоку в режимі «бездіяльності» транзистора, виникнення якого пов'язане з частковим «пробоєм» матеріалу каналу затвора, а також матеріалу підкладки. У новітній презентації 65-нм технології не зустрічається жодної згадки цього, досить важливого моменту, вірніше, по всій видимості, в представлених діаграмах IOFF просто ... непомітно підміняється величиною IGate. У той же час, з літературних даних добре відомо, що зменшення довжини затвора неодмінно тягне за собою збільшення сили струму IOFF. що, до речі, не заперечує і сама Intel в ряді інших презентацій.

Проблема витоку струму в стані спокою (IOFF). зверху # 151; пояснення суті проблеми. знизу # 151; співвідношення ION / IOFF для 90-нм і 65-нм транзисторів, за даними останньої презентації 65-нм технології (зліва) і залежність сили струму IOFF від розміру каналу затвора, за даними презентації «транзисторів майбутнього» Intel (праворуч). Невідповідність даних по IOFF. взятих з двох різних презентацій однієї і тієї ж компанії, як то кажуть, «у наявності».

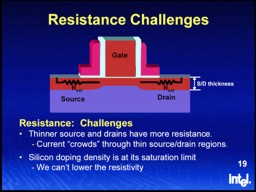

Проблема збільшення електричного опору матеріалу витоку і стоку при зменшенні розміру. Її рішення в 65-нм технологічному процесі представляється у вигляді застосування силіциду нікелю (NiSi) для виготовлення покриття даних компонентів транзистора поряд з покриттям затвора.

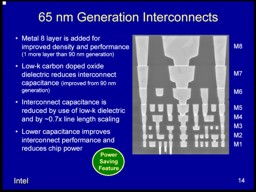

3. 8-шарові межтранзісторние з'єднання

Новий технологічний процес також вносить зміни в схему виготовлення сполучних ділянок. Перш за все, доданий ще один, восьмий металевий (мідний) шар, що забезпечує подальші збільшення щільності контактів і швидкості поширення електричних сигналів. В якості діелектрика як і раніше використовується low-k оксидний матеріал, допирований вуглецем (CDO), але відзначається, що технологія його виготовлення була поліпшена в порівнянні з поточним 90-нм техпроцесом. Застосування подібного матеріалу в поєднанні з новою методикою 0.7-кратного масштабування ліній мідних з'єднань призводить до подальшого зниження «міжконтактного» ємності, яке, як було зазначено в попередньому розділі, призводить до зниження потужності, що розсіюється на межтранзісторних з'єднаннях.

65-нм межтранзісторние з'єднання. Загальний вигляд і короткий опис технології їх виготовлення.

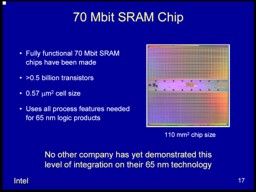

4. 0.57-мкм 2 осередки SRAM, транзистори «режиму сну»

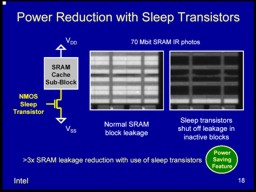

65-нм чіпи статичної пам'яті (SRAM). зліва # 151; вид чіпа і його технічні характеристики; справа # 151; енергозберігаючі властивості чіпа, пов'язані із застосуванням «транзисторів режиму сну»

Осередок 65-нм SRAM-чіпа є упаковку з 6 транзисторів (технологія 6T) і займає площу 0.57 мкм 2 (для порівняння, 90-нм кеш-пам'ять SRAM має площу 6T-осередки 1.0 мкм 2) і характеризується порівняно низьким статичним шумовим порогом (Static Noise Margin, SNM), що дозволяє оперувати пристрою при напрузі аж до 0.7 В.

Як наголошується в презентації 65-нм технології, важливою відмінністю нових 65-нм чіпів SRAM є використання так званих «транзисторів режиму сну», контролюючих протягом струму до субмассівам осередків SRAM в залежності від їх стану (подача напруги до даного набору осередків відключається при його бездіяльності , і включається при здійсненні звернення до одного з елементів цього набору). Очевидно, що наслідком застосування «транзисторів режиму сну» є значне скорочення споживання електроенергії підсистемою кеш-пам'яті процесора, що особливо важливо для мобільних пристроїв. Незважаючи на те, що дана технологія вважається відмінною рисою саме 65-нм пристроїв статичної пам'яті, не можна не помітити, що подібна (ми не стверджуємо, що саме така) технологія, насправді, вже давно реалізована і використовується ще з часів 130-нм мобільних процесорів Pentium M з ядром Banias, які вміють «присипляти» невикористовувані ділянки свого L2-кеша.

5. 300-мм виробничі підкладки

У виробництві 65-нм чіпів використовуються ті ж самі 300-мм підкладки, що застосовуються у виробництві поточного покоління 90-нм ядер процесорів. Дослідне виробництво самих 65-нм пристроїв в даний час здійснюється на фабриці D1D в Хілсбро, Орегон, де і був розроблений даний технологічний процес.

Основні завдання найближчого майбутнього напівпровідникових технологій Intel

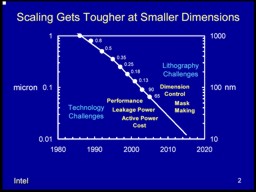

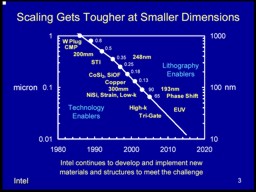

технологічні завдання

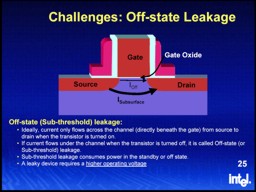

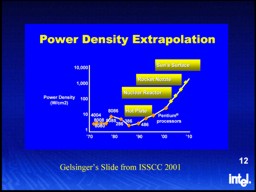

Які ж основні технологічні завдання майбутнього напівпровідникових технологій? Серед найважливіших, Intel відзначає наступні: продуктивність (очевидно, маючи на увазі все більшу і більшу трудність їх так полюбляють ними «нарощування частоти» або «погоні за гигагерцами»), проблема зниження струму витоку і «ціни» подальшого збільшення корисної потужності (збільшення співвідношення ION / IOFF).

Трехзатворние (tri-gate) транзистори

Проблема струму витоку

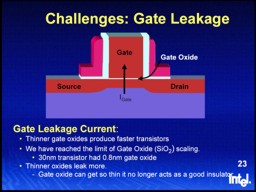

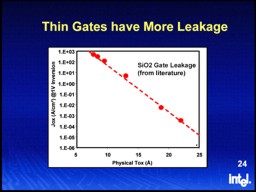

Як вже зазначалося вище при розгляді сучасного 90-нм і майбутнього 65-нм технологічних процесів, в якості матеріалу діелектричного шару затвора ось уже на протязі 30 років використовується діоксид кремнію (SiO2), головним чином, завдяки можливості збільшення швидкості роботи транзисторів за допомогою скорочення товщини утвореного їм ізолюючого шару. Проте, подальше скорочення товщини оксидної прошарку (а товщина 1.2 нанометра, що застосовується в 90-нм і 65-нм техпроцесах, становлять лише 5 атомних шарів!) Неминуче супроводжується появою небажаних ефектів, перш за все # 151; збільшенням струму витоку через діелектрик затвора (IGate), що проявляється у вигляді значного зростання енергоспоживання і розсіюється, а також «аномального» поведінки транзистора (відзначимо, що саме завдяки цим проблемам 90-нм процесор Pentium 4 Prescott з тактовою частотою 4.0 ГГц так і не побачив світло і був недавно остаточно виключений з планів розробки).

Проблема витоку струму через затвор (IGate). зліва # 151; пояснення суті проблеми; справа # 151; залежність сили струму витоку від товщини оксидного шару затвора.

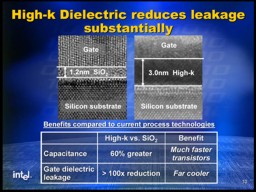

Для вирішення цієї критичної завдання Intel планується заміна поточного матеріалу діелектричного покриття затвора (SiO2) більш товстим шаром матеріалу з високою діелектричної постійної (high-k), що має кращі ізолюючі властивості, а також створює високу ємність між затвором і каналом транзистора (як стверджує Intel, назва «high-k» бере свій початок саме від виразу «high capacitance»). Перше властивість такого матеріалу значно знижує струм витоку, тобто споживану транзистором «пасивну» потужність, а друге дозволяє значно збільшити швидкість перемикання його станів. В якості бажаної high-k матеріалів в літературі зазначається використання оксидів цирконію і гафнію.

Застосування діелектриків з високою діелектричної постійної (high-k) в якості матеріалу ізолюючого шару затвора.

літографічні завдання

Серед літографічних завдань майбутнього Intel відзначає проблеми контролю розміру елемента і виготовлення масок. Перш ніж перейти до короткого розгляду цих проблем і їх рішень, зупинимося трохи докладніше на процесі літографії в цілому.