Процедура розгляду заяв про процесора лягає на набір системної логіки (так само званий чіпсетом), серед іншого включає в себе і контролер пам'яті. Контролер пам'яті повністю "прозорий" для програміста, проте знання його архітектурних особливостей істотно полегшує оптіміза-цію обміну з пам'яттю.

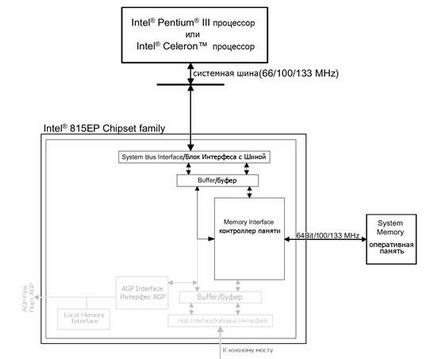

Пристрій північного моста чіпсета Intel 815EP, що містить (серед іншого) контролер пам'яті

Контролер шини (BIU - Bus Interface Init), "імплантований" в північний міст чіпсета, отримавши запит від процесора, в залежності від ситуації або передає його відповідному агенту (в нашому випадку - контролеру па-мяти), або ставить запит в чергу, якщо агент в цей момент чимось зайнятий. Потреба в черзі пояснюється тим, що процесор може посилати черговий запит, не чекаючи завершення обробки попереднього, а раз так, то запити доводиться десь зберігати.

Залежно від архітектури контролера пам'яті він працює з пам'яттю або тільки на частоті системної шини (синхронний контролер), або під-тримувати пам'ять будь-якої іншої частоти (асинхронний контролер). Сін-Хроні контролери обмежують користувачів ПК у виборі модулів пам'яті, але, з іншого боку, асинхронні контролери менш виробляй-тельно. Чому? По-перше, в силу невідповідності частот, читаються дані не можуть бути безпосередньо передані на контролер шини, і їх прихо-диться спочатку складати в проміжний буфер, звідки шинний контролер зможе їх витягати з потрібною йому швидкістю. (Аналогічна ситуа-ція спостерігається і з записом.) По-друге, якщо частота системної шини і частота пам'яті не співвідносяться як цілі числа, то перед початком обміну доводиться чекати завершення поточного тактового імпульсу. Таких затримок (в просторіччі пенальті) виникає дві:

при передачі лічених даних шинному контролера.

Все це значно збільшує латентність підсистеми пам'яті - т. Е. Про-проміжку часу з моменту посилки запиту до отримання даних. Таким чином, асинхронний контролер, який працює з пам'яттю SDRAM PC-133 на системній шині в 100 МГц, програє своєму синхронного побратимові, що працює на тій же шині з пам'яттю SDRAM PC-100.

Контролер шини, отримавши від контролера пам'яті повідомлення про те, що запитані дані готові, чекає звільнення шини, і передає їх процесору в пакетному режимі. Залежно від типу шини за один такт може передаватися від однієї до чотирьох порцій даних. Так, в про-цессора КБ, Р-І і Р-Ш здійснюється одна передача за такт, в процесорі Athlon - дві, а в процесорі Р-4 - чотири.

З цього моменту дані надходять в кеш і стають доступними процесору.

Контролер системної шини, що відповідає за обробку запитів і переме-щення даних між процесором і чіпсетом, складається з наступних функціональних компонентів: трансферу даних (Processor Source Synch Clock Transceiver), планувальника запитів (Command Queue - CQ), контролле-ра черг запитів (Control System Queue - CSQ) і агента транзакцій - XCA). Інші компоненти контролера ши-ни, присутні на рис. 2.11, необхідні для підтримки зондовой від-ладком, яка до обговорюваної теми не відноситься, а тому тут не рас-розглядати.

Трансфер даних - в якомусь вищому сенсі являє собою "голий" контролер шини, що розуміє шинний протокол і бере на себе всі турботи по спілкуванню з процесором. Отримані від процесора запити пе-Реда планувальником запитів, звідки вони відправляються відповідаю щим агентам в міру їх звільнення.

Відповіді агентів зберігаються в трьох роздільних чергах: черги читання (SysDC Read Queue - SRQ), черги записи пам'яті (Memory Write Queue - MWQ) і черги записи шини PCI (PCI / A-PCI Write Queue - AWQ). Зверніть увагу: в даному випадку мова йде про записі / читанні в процесор, а не на-оборот! Таким чином, черга записи пам'яті зберігає дані, що передаються-мі з пам'яті в процесор, але не записуються процесором в пам'ять!