симулятор ModelSim

Хочу розповісти трохи про симуляцію цифрових проектів. Так Так. Тема ця вже піднімалася кілька разів, і, звичайно - це невичерпна тема. Я вже колись писав про симуляцію засобами Quartus II версії 9. але в останній версії Quartus II v10 цього «рідного» альтеровского симулятора вже немає. Сказати по правді я засмутився. Для маленьких проектів цього симулятора цілком вистачало. Потім я написав статтю про симулятор iverilog - це простий open source симулятор - цілком пристойна річ. І ось тепер хочу коротко розповісти про програму ModelSim:

Я буду розповідати про одну з його версій, а саме ModelSim Altera Starter Edition.

Там побачите таблицю порівняльних характеристик різних версій ModelSim:

Ми вибираємо Starter Edition - вона безкоштовна, не вимагає ліцензії, може використовуватися на невеликих проектах до 10000 рядків коду. Я думаю, що нам це з головою вистачить. Переходимо по посиланню Download. Я вибираю версію для Windows. Розмір файлу, який потрібно завантажити - 586Мб. Це не мало, але і не дуже багато як на теперішній час. Загалом качаю і встановлюю ..

Я зараз хочу просімуліровать той же приклад, який я вже успішно пробував симулювати за допомогою iverilog. Це два файли counter.v і tcounter.v - вони розташовані у мене в папці c: \ altera \ 10.0 \ projects \ first.

Вміст цих файлів ось таке:

counter.v - це лічильник з можливістю паралельної завантаження. Якщо сигнал wr активний в момент фронту clk. то в регістр лічильника буде записано число з вхідний шини wdata. Інакше значення лічильника буде збільшуватися на одиницю кожен фронт clk.

module counter (

input wire reset,

input wire clk,

input wire [7: 0] wdata,

input wire wr,

output reg [7: 0] data

);

always @ (posedge clk or posedge reset)

if (reset)

data <= 8'h00;

else

if (wr)

data <= wdata;

else

data <= data + 8'h01;

А ось це - vcounter.v - "тестбенч" для мого лічильника. Ця програма служить для перевірки правильності роботи модуля counter.

`Timescale 1ns / 100ps

module test_counter;

reg reset, clk, wr;

reg [7: 0] wdata;

wire [7: 0] data_cnt;

counter counter_inst (reset, clk, wdata, wr, data_cnt);

initial

begin

clk = 0;

reset = 0;

wdata = 8'h00;

wr = 1'b0;

# 50 reset = 1;

# 4 reset = 0;

# 50;

@ (Posedge clk)

# 0

begin

wdata = 8'h55;

wr = 1'b1;

end

@ (Posedge clk)

# 0

begin

wdata = 8'h00;

wr = 1'b0;

end

end

initial

begin

# 400 $ finish;

end

initial

begin

$ Dumpfile ( "out.vcd");

$ Dumpvars (0, test_counter);

$ Dumpvars (0, counter_inst);

end

initial

$ Monitor ($ stime. Reset. Clk. Wdata. Wr. Data_cnt);

Ось ці файли я спробую використовувати для демонстрації роботи ModelSim.

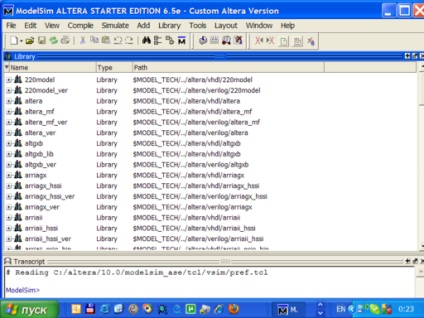

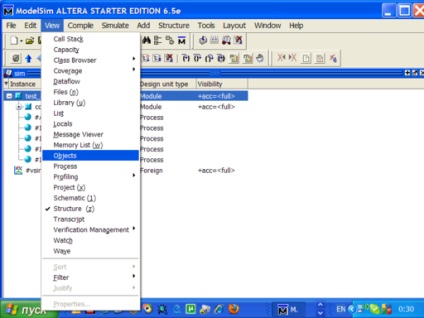

При запуску програми ModelSim ми бачимо приблизно ось такий екран (клікніть на зображення, щоб побачити його крупніше):

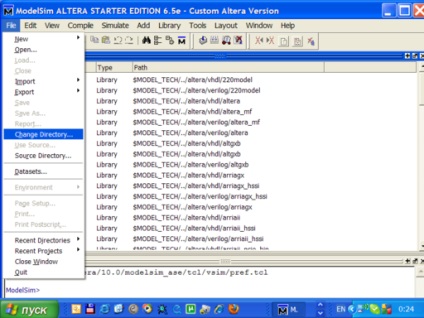

Перше, що нам потрібно зробити - це перейти в робочу папку. Для цього вибираємо пункт меню File / Change Directory.

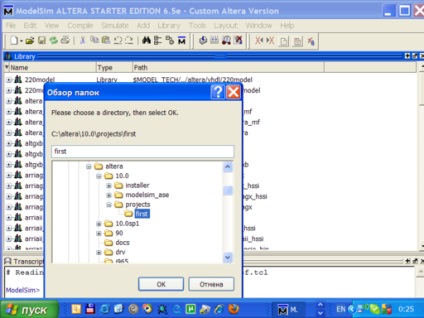

У діалозі вказуємо шлях до нашого проекту:

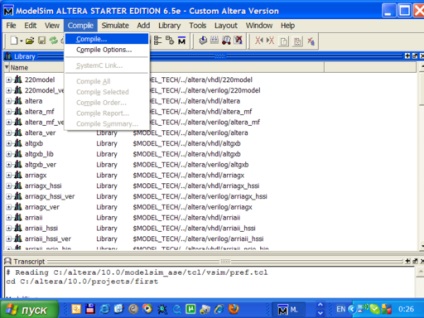

Після вибору папки потрібно скомпілювати проект в бібліотеку. Вибираємо пенкт меню Compile / Compile.

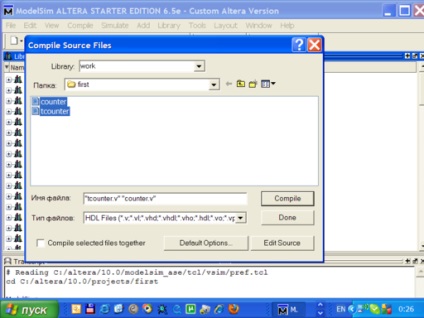

Тут потрібно вибрати всі файли нашого проекту. Діалог дозволяє вибирати одночасно декілька файлів.

Вибрали файли - натискаємо кнопку Compile.

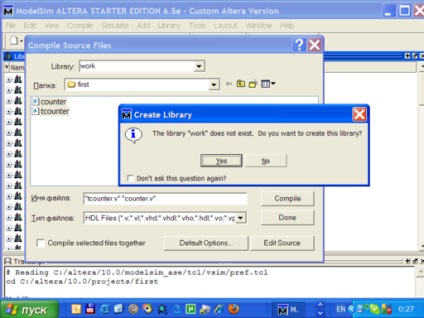

ModelSim запитує ім'я бібліотеки, яка буде створена. За замовчуванням пропонується ім'я work. ну ось нехай таке і буде. Відповідаємо Yes. Після компіляції в вікні Transcript перевіряйте, чи немає помилок у вихідних файлах.

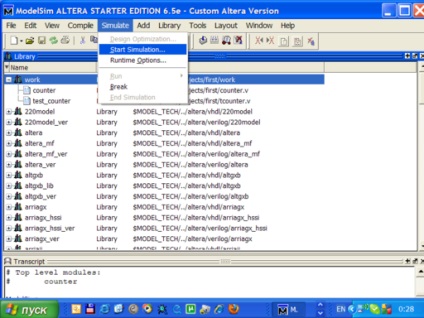

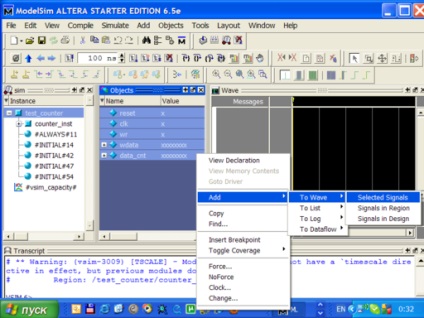

Зверніть увагу, що у вікні Library з'явилася нова бібліотека work. так і має бути. Тепер вибираємо пункт меню Simulate / Start Simulation.

Ось тепер і подивимося, що у нас виходить в симуляції. Робимо кілька кроків симуляції вперед за допомогою пункту меню Simulate \ Run \ Run100.

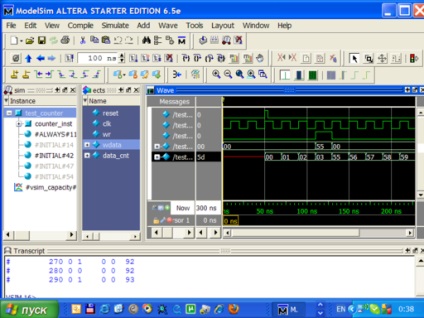

А ось і результат симуляції:

Зверніть увагу, що і текстовий висновок у вікні Transcript і самі сигнали в вікні Wave точно такі ж як і в випадку симуляції за допомогою open source icarus-verilog.

Ну і ось - за формою сигналів ми бачимо, що наш лічильник працює правильно - так як і було задумано нами!

Хто-небудь допоможіть встановити Modelsim на ubuntu.Прі запуску видає "./vish: error while loading shared libraries: libXft.so.2: can not open shared object file: No such file or directory".

спробуйте встановити додаткові бібліотеки sudo apt-get install libxft2

Хто-небудь допоможіть встановити Modelsim на ubuntu.Прі запуску видає "./vish: error while loading shared libraries: libXft.so.2: can not open shared object file: No such file or directory".

Цитую Молин Дмитро:

Така ж проблема, як у Vadim і Ia.

Моделс видає прямі лінії, при тому, що робив все, як написано в статті. Так само писав свої програми і навіть намагався подивитися на роботу елементів зі стандартних бібліотек, але результат один і той же.

Було то ж, вирішилося в такий спосіб: при виконанні Simulate \ Start Simulation потрібно вибрати тільки один файл тестбенча, я спочатку обидва вибирав - були прямі лінії. Щоб імпульси були схожі на ті, що на скріншотах, можна зменшити масштаб графіка (правою кнопкою - далі знайдете).

Зрозумів - якщо поставити обидва модуля (тестуючи мий і тестбенч) в одному файлі, то ModelSim не зможе відобразити результатів симуляції. Ну а взагалі таке можливо?

Використовуємо тип wire для моделювання вихідного сигналу, а не reg тільки потім, щоб не "зберігати" стан сигналу в регістрі і уникнути апаратних витрат?

Господа, хіба мало хто відповість, при прочитанні статті з'явилося пара дурних питань:

1) Чи можна тестбенч писати в тому ж файлі, що і тестовий модуль, просто тестбенч буде реалізований в якості іншого модуля? (Знаю знахабнів бо це можна легко нагугліть, але хіба мало кому не в тягар)

2) Навіщо створювався (був оголошений) сигнал wire [7: 0] data_cnt в тестбенче?

Чи правильно я зрозумів:

counter counter_inst (re set, clk, wdata, wr, data_cnt); - цим рядком ми створюємо інстанси модуля counter і підміняємо вихідний регістр data сигналом data_cnt? і який сенс цієї дії, чому не можна було замінити сигналом з тим же ім'ям data або навіть регістром data, як в тестованому модулі? Чи може взагалі регістр бути виходом тестбенча, або завжди необхідний тільки сигнал, як вихід?

Така ж проблема, як у Vadim і Ia.

Моделс видає прямі лінії, при тому, що робив все, як написано в статті. Так само писав свої програми і навіть намагався подивитися на роботу елементів зі стандартних бібліотек, але результат один і той же.

Було то ж, вирішилося в такий спосіб: при виконанні Simulate \ Start Simulation потрібно вибрати тільки один файл тестбенча, я спочатку обидва вибирав - були прямі лінії. Щоб імпульси були схожі на ті, що на скріншотах, можна зменшити масштаб графіка (правою кнопкою - далі знайдете).