MIPS була однією з перших RISC-архітектур, які отримали визнання промисловості

Корпорація SGI (www.sgi.com) одна з небагатьох комп'ютерних компаній, яка розробляє обчислювальні системи від початку до кінця, т. Е. Від створення мікропроцесорів (MIPS) і архітектури обчислювальної системи до написання ОС (IRIX) і ПО. Очевидно, саме тому користувачами комп'ютерних систем SGI є багато військових і державних установ США, великі дослідницькі центри і корпорації.

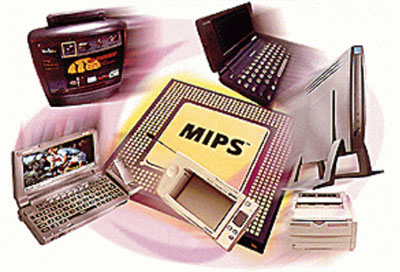

Архітектура MIPS (Microprocessor without Interlocked Pipeline Stages), запропонована фахівцями SGI / MIPS Technologies, була однією з перших RISC-архітектур, які отримали визнання промисловості. В даний час вона ліцензована найбільшими виробниками напівпровідникових пристроїв, серед яких Broadcom, IDT, LSI Logic, NEC, NKK, Philips і Toshiba. Розроблено спеціальний стандарт, що забезпечує переносимість бінарних додатків між різними MIPS-платформами, які діють під управлінням ОС UNIX. У MIPS Technologies, мабуть, самий тривалий досвід роботи з 64-розрядними архітектурою, а що випускаються нею мікропроцесори підтримують створення SMP-архітектур з пам'яттю, що з десятків мікропроцесорів. Користувачів дуже приваблює орієнтація цієї архітектури на застосування мультимедіа та високоякісні засоби візуалізації зображень. Досить часто мікропроцесори цього сімейства зустрічаються у вбудованих контролерів.

Вони були першими

Процесори R3000 / R3010 мали стандартні п'ятиступінчасті конвеєри команд і працювали на тактових частотах 33 і 40 МГц. На зміну сімейству R3000 прийшли 64-розрядні мікропроцесори R4000 і R4400. Варто відзначити, що MIPS Technologies - перша компанія, що випустила процесори з 64-розрядної архітектурою. Набір команд цих пристроїв було розширено командами завантаження і запису 64-розрядних дійсних чисел, обчислення квадратного кореня з одинарної і подвійний точністю, умовних переривань, а також операціями, необхідними для підтримки мультипроцесорних конфігурацій. У процесорах R4000 і R4400 реалізовані 64-розрядні шини даних і 64-розрядні регістри. Саме в цих процесорах застосовується метод подвоєння внутрішньої частоти. У сімействі R4х00 використовувалися довші конвеєри (іноді їх називали суперконвейерамі), число ступенів у яких було збільшено до восьми, що пояснювалося насамперед збільшенням тактової частоти і необхідністю розподілу логіки для забезпечення заданої пропускної здатності. Процесори R4х00 могли працювати з тактовою частотою від 50 до 100 МГц.

Внутрішня кеш-пам'ять процесора R4000 мала ємність 16 Кб. Вона поділялася на 8 Кб для команд і 8 Кб для даних. Відмінною особливістю сімейства чіпів R4x00 стали спеціальні алгоритми забезпечення когерентності кеш-пам'яті в багатопроцесорних конфігураціях. Зокрема, архітектура мікропроцесора R4400 дозволяла за один такт звернення до пам'яті записати або прочитати або одне дійсне число (з плаваючою комою), або дві інструкції. Завдяки цьому внутрішній конвеєр ядра працював з подвоєнням частоти.

Наступний крок у створенні високопродуктивних систем - випуск процесора R10000. Завдяки наявності декількох оброблювальних пристроїв даний кристал зміг виконувати дві цілочисельні команди і дві операції над числами за один такт, що забезпечило йому підвищену продуктивність на тактовій частоті 200 МГц. При цьому обмін даними з кеш-пам'яттю другого рівня здійснювався зі швидкістю 3,2 Гб / с.

Особливості архітектури R1x000

При розробці процесора R10000 велику увагу було приділено ефективної ієрархії пам'яті. Зокрема, в даному кристалі забезпечується раннє виявлення промахів кеш-пам'яті з виконанням іншої корисної роботи. Так, кеш-пам'ять підтримує одночасну вибірку і виконання команд завантаження і запису даних в пам'ять, а також операції перезавантаження рядків кеш-пам'яті. Робота конвеєрів кеш-пам'яті даних тісно координована. При виявленні промаху при зверненні до кеш-пам'яті даних її робота не блокується, отже, вона може продовжувати обслуговування наступних запитів.

Архітектура R1х000 включає 64 фізичних регістра. У процесорі є п'ять повністю незалежних виконавчих пристроїв: два цілочисельних, два речової арифметики, а також пристрій завантаження / запису.

Час виконання всіх цілочисельних операцій, за винятком операцій множення і ділення, становить один такт. Цілочисельні операції множення виробляють твір з подвійною точністю. Для операцій з одинарної точністю відбувається поширення знака результату до 64 розрядів перш, ніж він буде поміщений в регістри. Операції з подвійною точністю виконуються приблизно в два рази швидше операцій з одинарної точністю.

Крім основних пристроїв речової арифметики існують два додаткових, які обробляють довгі операції ділення і обчислення квадратного кореня. Пристрій завантаження / запису виконує команди завантаження, записи, попередньої вибірки, а також інструкції для роботи з кеш-пам'яттю. Зовнішня кеш-пам'ять другого рівня управляється за допомогою внутрішнього контролера, який має для цієї мети спеціальний порт. За магістралі шириною в 128 розрядів здійснюються пересилання даних на внутрішній тактовій частоті 200 МГц. Системний 64-розрядний інтерфейс R10000 використовується в якості шлюзу між самим процесором, пов'язаним з ним кеш-пам'яті другого рівня, і рештою системи. Мікросхема R10000 допускає два способи організації багатопроцесорної системи.

перспективні плани

Мікропроцесори MIPS стали свого часу одними з перших 64-розрядних мікропроцесорів і були в числі лідерів по продуктивності. Однак стратегічне рішення орієнтуватися в перспективі тільки на 64-розрядну архітектуру Intel, прийняте свого часу керівництвом SGI, виявилося помилковим. Численні затримки з випуском Itanium привели до втрати корпорацією лідируючих позицій в галузі створення RISC-кристалів. Мабуть, ця подія змусило керівництво SGI знову зайнятися розробкою чергових моделей сімейства R1x000.