Нещодавно два мікропроцесорних гіганта - Intel і AMD - дружно випустили свої перші двоядерні процесори, які вже встигли наробити багато шуму. Нові мікропроцесори вийшли не просто цікавими, але є вельми багатогранні продукти, ретельне дослідження яких не може обмежитися одним-двома оглядами, написаними по гарячих слідах. Ми постараємося розповісти про ці нові продукти більш детально і, по можливості, з різних сторін.

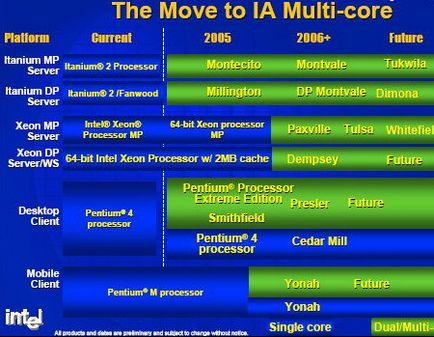

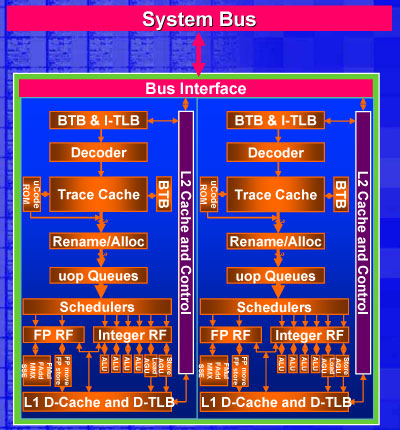

Поки ж ми маємо від Intel тільки Smithfield - найпростіші «двопроцесорні процесори» - мова навіть не повертається говорити про «ядрах». Все нудно до неможливості (втім, далеко не завжди рухає прогрес то, що «весело» :)) ... І, на жаль, є несумісним з усіма вже існуючими чіпсетами самої Intel, бо чіпсети, розраховані на однопроцесорних шину, тепер змушені будуть працювати фактично з «дуальними» системами, а двопроцесорним чипсетам (нагадаємо, що Intel чітко розділяє процесори «для дуалов» і для «багатопроцесорних систем») доведеться навчитися працювати з «квадами» - четвірками процесорів. Тобто навантаження на системну шину істотно зросте і колишні чіпсети на неї по-справжньому просто не розраховані. До речі, в Intel пробували запускати Smithfield на чіпсетах серії i925 / 915, але робота такої зв'язки не завжди була досить стабільною, тому від неї було вирішено офіційно відмовитися і навіть передбачити заходи, що виключають запуск двоядерних процесорів на платах зі старими чіпсетами.

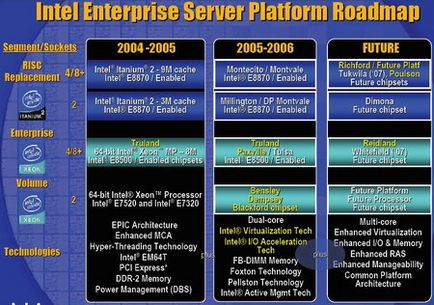

Аналогічно двоядерний «відгукнулася» і в лінійці Intel Xeon - частково саме через збільшення навантаження на шину QPB, яку використовують ці двоядерні процесори, Intel і затримується з випуском двоядерних Xeon MP для чотирьох і більше процесорних систем, вважаючи за краще розробити для них новий 90- нм кристал Paxville, який буде мати загальний на два процесорних ядра контролер системної шини (щоб знизити навантаження на неї), хоча кеш-пам'ять і раніше буде своя у кожного з ядер. Двопроцесорні ж Xeon на перших порах залишаться суто «двухкрістальнимі» Dempsey.

Платформа на Paxville

«Класична» двухпроцессорная SMP-система з двоядерними процесорами

Нарешті, відзначимо, що організація «системи в цілому» у Intel настільки ж традиційна, як і пристрій двоядерного процесора. У ній є кілька «рівноправних» центральних процесорів (як правило, поділяють загальну шину); є оперативна пам'ять і є різного ступеня швидкодії периферія. Весь цей комплект об'єднується в єдине ціле спеціальним комунікаційним процесором - «північним мостом» (Northbridge) чіпсета. Через нього проходять буквально все потоки даних, які тільки зароджуються в комп'ютері. Образно кажучи, якщо «процесори» - це «голови» комп'ютера, то північний міст - це його серце. Подібний «централізований» підхід, по-перше, відрізняється відносною простотою, а по-друге, зручний тим, що в ньому кожен компонент комп'ютера виходить вузькоспеціалізованим, і піддається модернізації незалежно від інших компонентів. Тобто з одним і тим же Northbridge можна використовувати, наприклад, абсолютно різні за своєю продуктивністю і навпаки - змінюючи Northbridge, можна, наприклад, використовувати з одним і тим же процесором абсолютно різні типи оперативної пам'яті.

Трохи про термінологію

Уважні читачі вже звернули увагу на «загадкові» блоки з підписами APIC, DMA, GART ... що всі вони означають?

• DMA (Direct Memory Access) - це такий своєрідний «альтернативний процесор», який займається в чіпсеті обробкою «фонових» завдань, пов'язаних з периферією. Скажімо, якщо процесору потрібно прочитати пару кілобайт даних з жорсткого диска, то йому зовсім не обов'язково терпляче чекати цілу вічність (кілька мілісекунд), поки ці самі дані йому не будуть надані. Замість цього він може запрограмувати DMA-контролер, щоб той виконав це завдання за нього, і переключитися, поки цей запит виконується, на якусь іншу задачу. Штука це не настільки незамінна, як APIC, але без неї не було б навіть інтерфейсу Ultra ATA / 33

AMD Toledo: SUMA, SRI і інтегрований Northbridge

Архітектура AMD K8 не просто відрізняється від «интеловской»: вона концептуально інша, оскільки в ній немає якогось виділеного центру. Кожен з процесорів архітектури AMD64 є незалежною і «самодостатньою» одиницею, яка об'єднує в собі майже всю функціональність північного моста традиційних наборів системної логіки. Це почалося з одноядерних процесорів, а з появою двух'ядернік «обросло» новими відзнаками. Погляньмо на блок-схему двухпроцессорной системи на двоядерних AMD Opteron.

Приклад двухпроцессорной двоядерний системи на Opteron 2xx і чіпсеті AMD 81xx. HT позначає HyperTransport

Якщо дивитися на це питання з чисто технічної сторони, то AMD просто інтегрувала практично всю функціональність північного моста в центральний процесор. На блок-схемах в «даташітах» так і позначається: ось власне процесорний ядро, ось HT-інтерфейс, а ось тут у нього Northbridge. Але «невелика» технологічна уловка призводить до зовсім іншої архітектури комп'ютера - SUMA, на відміну від традиційної SMP. Перерахуємо коротко основні переваги SUMA над «класичної» SMP.

• Шина HT спеціально оптимізувалася для подібного режиму роботи з безліччю «службових» повідомлень (які виникають при використанні MOESI, про який ми розповімо трохи пізніше) і забезпечує вкрай низьку латентність звернення в «чужу» пам'ять і високу (до 4 Гбайт / с) пропускну здатність при зверненні до пам'яті «сусідів». Шина є полнодуплексной, тобто шина дозволяє одночасно передавати дані на цій швидкості в «обидві сторони» (до 8 Гбайт / с сумарно). Модель пам'яті стає неоднорідною (NUMA), але відмінності в швидкості «своїх» і «чужих» ділянок оперативної пам'яті виходять відносно невеликими.

• чіпсет сильно спрощується: все, що від нього вимагається - це просто забезпечувати «мости» (тунелі) між HT і іншими типами шин. Ну і, можливо, заодно забезпечувати якусь кількість інтегрованих контролерів. Особливо яскраво цей принцип проявляється в серверному чіпсеті AMD 81xx, оскільки це просто набір з двох чіпів - «перехідників» на шини AGP і PCI-X і чіпа, інтегруючого тунель на «звичайну» PCI і стандартний набір периферійних контролерів (IDE, USB, LPC та ін.). Втім, традиційні «великі» чіпсети теж ніхто використовувати не забороняє: наприклад, NVIDIA успішно випускає Force3 і nForce4, які об'єднують всі необхідні тунелі і контролери в єдиному кристалі. Але зате можна, наприклад, встановити на плату чіп nForce Professional 2200 (рішення «все-в-одному» від NVIDIA для робочих станцій) і додати до нього «в напарники» AMD 8132, який забезпечить материнської плати підтримку шини PCI-X, якої в nForce Pro 2200 немає. Або використовувати кілька чіпів nForce Pro 2200, щоб забезпечити, наприклад, удвічі більше число ліній PCI Express. Тут все сумісно з усім: будь-які сучасні чіпсети для мікроархітектури AMD64, теоретично, повинні працювати і з будь-якими процесорами AMD ... і будь-якими «правильно» зробленими «напарниками». І, зокрема, всі двоядерні процесори AMD повинні працювати з усіма раніше випущеними чіпсетами для процесорів архітектури K8.

AMD зараз любить підкреслювати, що її процесори «спеціально проектувалися в розрахунку на двоядерний», але, строго кажучи, правильніше було б говорити, що двоядерний дуже вдало лягає на її архітектуру. Кожен процесор K8 є «системою в мініатюрі», зі своїм «процесором» і Northbridge; а двоядерний K8 - «двухпроцессорная SMP-система в мініатюрі».

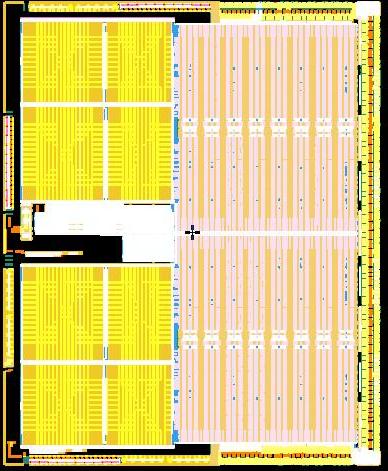

Кристал двоядерного процесора AMD

Друге ядро підключається до крос-бару через загальну шину SRI; обидва ядра ідентичні і, фактично, є повноцінними процесорами; загального кеша L2 немає. Тобто якщо ми, скажімо, розглядаємо однопроцесорних двоядерний систему, то вся різниця між реалізаціями AMD і Intel з «технологічної» точки зору полягає в тому, що у Intel Northbridge реалізований окремим кристалом, а у AMD він просто інтегрований в центральний процесор. Але ...

... Але інтеграція Northbridge в процесор і SUMA-архітектура K8 не просто забезпечує «швидший контролер оперативної пам'яті», - вона заодно дозволяє дуже ефективно вирішувати і ряд властивих багатопроцесорним системам проблем.