Організація асинхронного послідовного обміну даними із зовнішнім пристроєм ускладнюється тим, що на передавальної і приймальні стороні послідовної лінії зв'язку використовуються налаштовані на одну частоту, але фізично різні генератори тактових імпульсів і, отже, загальна синхронізація відсутня. Розглянемо на прикладах організацію контролерів послідовних інтерфейсів для послідовних асинхронних передачі і прийому даних.

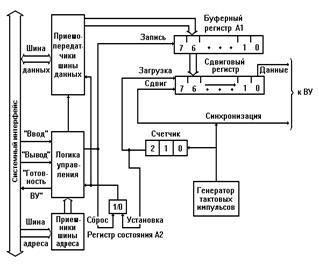

Найпростіший контролер для асинхронної передачі даних в ВУ по послідовної лінії зв'язку представлений на рис. 3.8. Він призначений для передачі даних в форматі з двома степових битами.

Мал. 3.8. Контролер послідовної асинхронної передачі

Після передачі чергового байта даних в регістр стану А2 записується 1. Одиничний вихідний сигнал регістра А2 інформує процесор про готовність контролера до прийому наступного байта даних і передачі його по лінії зв'язку в ВУ. Цей же сигнал забороняє формування імпульсів з схеми вироблення імпульсів зсуву - подільника частоти сигналів тактового генератора на 16. Лічильник імпульсів зсуву (лічильник по mod 10) знаходиться в нульовому стані і його одиничний вихідний сигнал надходить на вентиль І, готуючи ланцюг виробленнясигналу завантаження зсувного регістру .

Процес передачі байта даних починається з того, що процесор, виконуючи команду "Висновок", виставляє цей байт на шині даних. Одночасно процесор формує керуючий сигнал системного інтерфейсу "Висновок", щодо якого проводяться запис переданого байта в буферний регістр А1, скидання регістра стану А2 і формування на вентилі І сигналу "Завантаження". Передається байт переписується в розряди 1. 8 зсувного регістру, в нульовий розряд зсувного регістру записується 0 (стартовий біт), а в розряди 9 і 10 - 1 (стопові біти). Крім того, знімається сигнал "Скидання" з дільника частоти, він починає накопичувати імпульси генератора тактової частоти і в момент прийому шістнадцятого тактового імпульсу виробляє імпульс зсуву.

На вихідний лінії контролера "Дані" підтримується стан 0 (значення стартового біта) до тих пір, поки не буде вироблений перший імпульс зсуву. Імпульс зсуву змінить стан лічильника імпульсів зсуву і перепише в нульовий розряд зсувного регістру перший інформаційний біт переданого байта даних. Стан, що відповідає значенню цього біта, буде підтримуватися на лінії "Дані" до наступного імпульсу зсуву.

Аналогічно будуть передані інші інформаційні біти, перший стоповий біт і, нарешті, другий стоповий біт, при передачі якого лічильник імпульсів зсуву знову встановиться в нульове стан. Це призведе до запису 1 в регістр стану А2. Одиничний сигнал з виходу регістра А2 заборонить формування імпульсів зсуву, а також інформує процесор про готовність до прийому нового байта даних. Після завершення передачі чергового кадру (стартового біта, інформаційного байта і двох степових біт) контролер підтримує в лінії зв'язку рівень логічної одиниці (значення другого стопового біта).

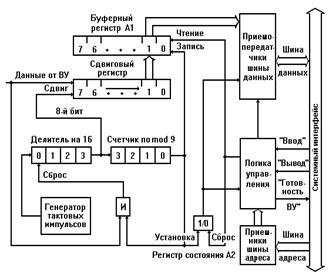

Мал. 3.9. Контролер послідовного асинхронного прийому

Рівень логічної одиниці надходить по лінії "Дані" в контролер для асинхронного прийому даних (рис. 3.9). Цей рівень створює умови для вироблення сигналу, що забороняє роботу дільника частоти генератора тактових імпульсів. Дійсно, після прийому попереднього байта даних лічильник імпульсів зсуву (лічильник по mod 9) знаходиться в нульовому стані і на вентиль І надходять два одиничні сигналу: з лічильника зрушень і з лінії "Дані". На виході вентиля І виробляється сигнал скидання дільника частоти сигналів тактового генератора, який забороняє формування імпульсів зсуву.

У момент зміни стопового біта на стартовий біт (момент початку передачі нового кадру) на лінії "Дані" з'явиться рівень логічного нуля і тим самим буде знято сигнал скидання з дільника частоти. Стан 4-розрядного двійкового лічильника (подільника частоти) почне змінюватися. Коли на лічильнику накопичиться значення 8, він видасть сигнал, що надходить на входи зсувного регістру і лічильника імпульсів зсуву. Так як частота сигналів генератора тактових імпульсів приймача повинна збігатися з частотою генератора тактових імпульсів передавача, то зрушення (зчитування) біта відбудеться приблизно на середині тимчасового інтервалу, відведеного на передачу біта даних, т. Е. Часу, необхідного для вироблення шістнадцяти тактовихімпульсів. Це робиться для зменшення ймовірності помилки через можливе відмінності частот генераторів передавача і приймача, спотворення форми переданих сигналів (перехідні процеси) і т. П. Наступний зрушення відбудеться після проходження шістнадцяти тактовихімпульсів, т. Е. На середині тимчасового інтервалу передачі першого інформаційного біта.

При прийомі в зсувний регістр дев'ятого біта кадру (восьмого інформаційного біта) з нього "висунеться" стартовий біт і, отже, в сдвиговом регістрі буде розміщений весь прийнятий байт інформації. У цей момент лічильник імпульсів зсуву прийде в нульовий стан і на його виході буде вироблений одиничний сигнал, по якому вміст зсувного регістру перепишеться в буферний регістр, в регістр стану А2 запишеться 1 і він буде інформувати процесор про закінчення прийому чергового байта, вентиль І підготується до виробленні сигналу "Скидання" (цей сигнал сформується після приходу першого стопового біта).

Отримавши сигнал готовності (1 в регістрі А2), процесор виконає команду "Введення" (див. Приклад 2.2 Паралельної передачі даних). При цьому виробляється керуючий сигнал системного інтерфейсу "Введення", щодо якого проводяться пересилання прийнятого байта даних з буферного регістра в процесор (сигнал "Читання") і скидання регістра стану А2.

Відзначимо, що для простоти викладу в контролері на рис. 14 не показані схеми контролю степових біт прийнятого кадру. Чи не показані також схеми контролю парності або непарності (паритету) переданої інформації (зазвичай в переданому байте восьмому біту надається значення 0 або 1, так щоб в цьому байті було парне кількість одиниць). У реальних контролерах є такі схеми, і якщо контролер не приймає з лінії зв'язку потрібної кількості степових біт або виробляється сигнал помилки паритету в схемі контролю парності, то прийняті в поточному кадрі біти даних ігноруються і контролер очікує надходження нового стартового біта.

Обмін даними з ВУ по послідовним лініях зв'язку широко використовується в мікроЕОМ, особливо в тих випадках, коли не потрібно високої швидкості обміну. Разом з тим застосування в них послідовних ліній зв'язку з ВУ обумовлено двома важливими причинами. По-перше, послідовні лінії зв'язку прості по своїй організації: два дроти при симплексной і полудуплексной передачі і максимум чотири - при дуплексной. По-друге, в мікроЕОМ використовуються зовнішні пристрої, обмін з якими необхідно вести в послідовному коді.

В сучасних мікроЕОМ застосовують, як правило, універсальні контролери для послідовного ВВ, що забезпечують як синхронний, так і асинхронний режим обміну даними з ВУ.