Одним з важливих і широко використовуваних цифрових елементів є лічильник. Ми спробуємо розібратися в тому, які лічильники бувають, і як їх спорудити з базових будівельних блоків цифрової схемотехніки. Мимохідь доведеться розглянути і суматори, оскільки вони будуть потрібні нам для створення синхронного лічильника. Що ж це за лічильник такий і що він вважає?

Функція лічильника, як неважко здогадатися, підрахунок кількості імпульсів, що надходять на його вхід. Перед початком роботи лічильник скидається відповідним сигналом (reset) і на його виході встановлюється n-розрядний двійковий код рівний нулю. За активного фронту тактового сигналу код на виході лічильника збільшується на одиницю. Крім цього, також можуть бути присутні сигнали дозволу і напрямки рахунки (зменшувати або збільшувати значення лічильника).

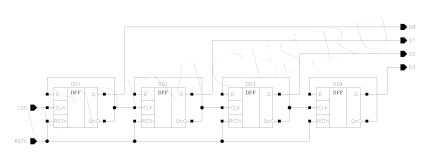

Раніше ми вже обговорювали недоліки асинхронного дизайну цифрових схем, але в якості прикладу все ж хочу показати варіант реалізації асинхронного лічильника (ripple counter). І хоча він простіше, ніж синхронний лічильник, і вимагає меншу кількість логічних елементів, ніколи не використовуйте його в своїх проектах! Це може призвести до виникнення помилок в роботі схеми і він може стати причиною появи незрозумілих глюків. На малюнку нижче представлена схема 4-розрядного асинхронного лічильника на двотактних D-тригерах:

Асинхронний лічильник являє собою послідовне з'єднання двотактних D-тригерів. За активного фронту тактового сигналу (CLK) відбувається інвертування стану першоготригера в ланцюжку (молодший розряд), т. Е. Вихід змінюється з 0 в 1 і навпаки. Тактовий сигнал кожного наступного тригера береться з виходу попереднього, таким чином, кожен наступний тригер перемикається в 2 рази рідше попереднього (DD2 перемикається кожен другий такт, DD3 - кожен четвертий такт і т. Д.). Ця схема асинхронна і виходи даних будуть оновлюватися по черзі в міру проходження сигналу по ланцюжку тригерів.

Структура синхронного лічильника трохи складніше. Крім n тригерів (n-розрядного регістра), йому необхідний n-розрядний суматор. Регістр зберігає результат рахунку, і по кожному такту до збереженого значення необхідно додавати одиницю (за допомогою суматора) і зберігати новий результат в регістрі. Перш ніж розглянути реалізацію такого лічильника, слід розібратися як працює акумулятор і як його реалізувати.

Суматор, як випливає з назви, просто складає два довічних числа. Додавання двійкових чисел відбувається так само, як і десяткових. В десяткової арифметики є 10 цифр - від 0 до 9. Якщо додати до 9 одиницю, то відбувається переповнення розряду (позиції) числа і відбувається перенесення одиниці в наступний розряд, таким чином, якщо до 29 додати 1, то молодший розряд переповниться, там виявиться 0, а одиниця переноситься в наступний розряд і додається до його значенням (2 + 1 = 3), отримуємо 30. Точно така ж логіка справедлива і для двійкових чисел.

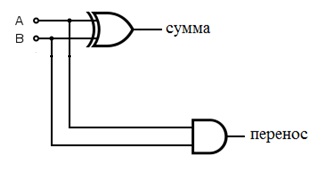

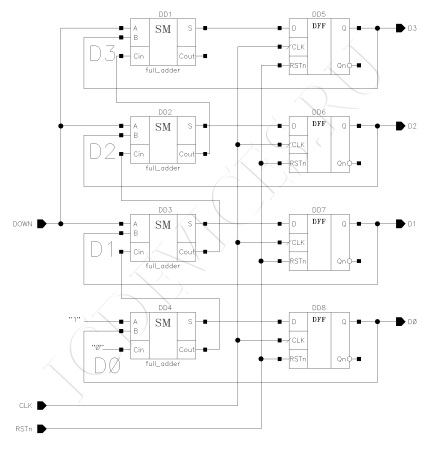

Для початку слід розглянути однорозрядних суматор. Як же його зробити з логічних елементів? Однорозрядних суматор має два входи (для доданків) і два виходи - сума і перенесення в наступний розряд (переповнення). Давайте спробуємо визначити, який логічної функції відповідає біт суми і біт перенесення. Очевидно, що перенесення в наступний розряд (біт C - Carry) з'являється тільки в тому випадку, якщо на вході будуть обидві одиниці, при цьому біт суми буде дорівнює 0, оскільки сталося переповнення розряду. Виходить, що біт суми є ні що інше, як виключне АБО входів суматора (подивіться на таблицю істинності виключає АБО і переконайтеся в цьому самі). При цьому, біт перенесення З являє собою логічне І входів (адже перенесення з'являється тільки при обох одиницях на вході).

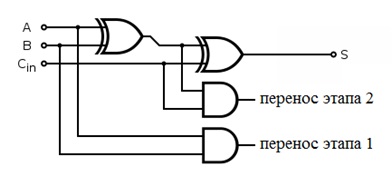

Ця схема називається полусумматора, оскільки не враховує біт перенесення з попереднього розряду, хоча сама формує перенесення в наступний розряд. Для обліку перенесення з попереднього розряду необхідно додати до суми А і В ще й біт перенесення з попереднього розряду, тобто додати другий полусумматор:

Таким чином, якщо перенесення сформувався хоча б на одному з полусумматора, то він повинен з'явитися на виході повного суматора. для цього можна застосувати логічне АБО.

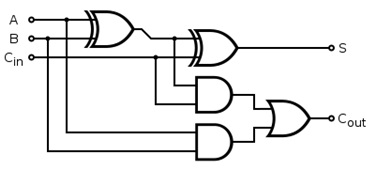

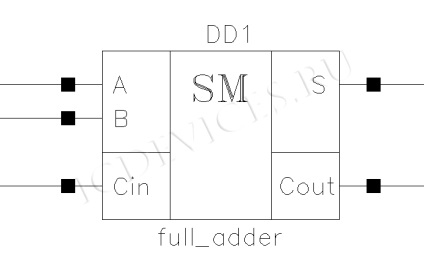

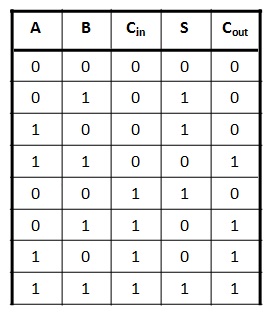

Однорозрядних повний суматор має три входи (два біта, які необхідно скласти в даному розряді і біт перенесення з попереднього розряду) і два виходи (біт суми і біт перенесення в наступний розряд).

Щоб реалізувати n-розрядний суматор, потрібно n повних суматорів. На їх входи А і В подаються відповідні розряди чисел, які необхідно скласти, а вхід Cin кожного розряду з'єднується з виходом Cout попереднього розряду, причому на вхід Cin молодшого розряду подається лог. 0. Нижче показана схема 4-розрядного суматора ([0] - молодший розряд, [3] - старший розряд):

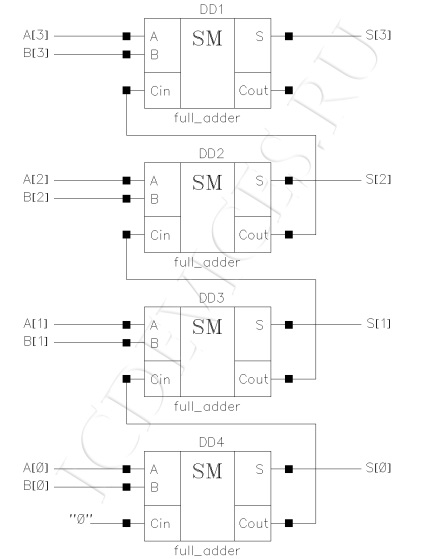

Тепер все готово для реалізації синхронного лічильника. Трохи ускладнити завдання і зробимо лічильник, який зміг би вести рахунок як в прямому, так і в зворотному напрямку. Введемо додатковий біт напрямку рахунку і якщо він дорівнює 0 - будемо додавати одиницю кожен такт, а якщо дорівнює 1 - віднімати одиницю кожен такт. Зі складанням все зрозуміло, але як відняти одиницю? Відняти одиницю з числа це те ж саме, що і додати до числа «мінус одиницю». Двійкові числа зі знаком представляються в так званому додатковому коді. Щоб отримати двійкове подання негативного числа необхідно інвертувати всі його розряди і додати до нього одиницю. Наприклад, 4-розрядне число «5» в двійковому вигляді виглядає як 0101, щоб отримати число «-5» інвертуємо біти - отримуємо 1010 і додаємо одиницю - отримуємо 1011. Тепер якщо скласти ці числа 5 і -5, то отримаємо: 0101+ 1011 = 10000, при цьому відбудеться переповнення, одиниця піде в наступний розряд, але ми її не враховуємо (цей розряд «відкидається»). Оскільки ми підсумовували 4-розрядні числа, то на виході побачимо тільки 4 молодших розряду, т. Е. 0000. Важливо відзначити, що в додатковому коді старший розряд визначає знак (одиниця - ознака негативного числа). Таким чином, в прямому коді 4-розрядних числом можна уявити десяткові числа від 0 до 15, а в зворотному коді від -8 до 7.

Отже, приступимо до реалізації 4-розрядного синхронного лічильника. Лічильник матиме 3 входу: тактовий сигнал, напрямки рахунки і сигнал скидання (обнулення). Поточне значення лічильника буде зберігається в регістрі (4 двотактних D-тригера). З виходу регістра поточне значення лічильника приходить на вхід суматора (скажімо, на вхід В). На інший вхід суматора (А) надходить значення «1» (0001) або «-1» (1111) в залежності від напрямку рахунку. На виході суматора з'являється нове значення, збільшене або зменшене на одиницю, яке надходить на вхід регістра. За активного фронту тактового сигналу це значення зберігається в регістрі і вихід лічильника оновлюється.

Якщо DOWN = 0, то на вхід A суматора надходить число 0001 (додаємо одиницю), в іншому випадку (DOWN = 1) на вході суматора виявляється число 1111 (віднімаємо одиницю). Зауважте, що всі тригери тактуються єдиним сигналом CLK. і все розряди лічильника оновлюються одночасно з активного фронту тактового сигналу. Важливо розуміти, що для правильної роботи схеми на виході суматора повинні встигнути з'явитися нові дані до наступного активного фронту CLK (затримка суматора не повинна перевищувати період тактового сигналу).

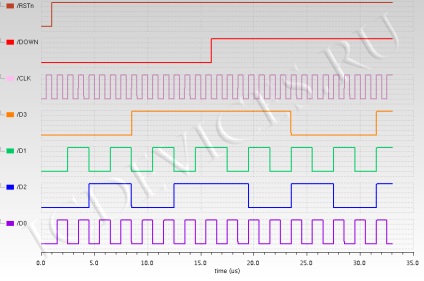

Тимчасова діаграма сигналів лічильника (лічильник скидається по низькому рівню сигналу RSTn. Про що свідчить суфікс «n»):

Ось ми і зробили найпростіший синхронний лічильник. Далі спробуємо описати його мовою Verilog і познайомимося з середовищем для моделювання ModelSim.