У міру того як нестача частотного спектра стає більш відчутною, необхідність його дбайливого використання зростає. У цих умовах необхідно підтримати високий рівень спектральної ефективності в усьому частотному діапазоні, виділеному для наземних бездротових служб. У статті розглядається метод цифрової обробки РЧ-сигналів (РЧ DSP), ефективно застосовується в непередбачуваною помеховой обстановці.

В існуючому різноманітті мікроконтролерів (МК) легко загубитися. У статті описана комплексна методика вибору відповідної моделі. Наведено практичні приклади і таблиці з основними характеристиками МК.

Гарвардська архітектура

Процесор Cortex-M4 побудований за гарвардської архітектурі, яка характеризується наявністю окремих шин команд і даних. Завдяки можливості одночасного читання команд і даних з пам'яті Cortex-M4 здатний виконувати багато операцій паралельно, що прискорює виконання програми. 32-розрядна шина AMBA AHB-Lite ICode вибирає команди з кодовою області пам'яті, а 32-розрядна шина AMBA AHB-Lite DCode здійснює доступ до даних з кодовою області пам'яті. Периферійні шини забезпечують доступ до компонентів поза системою процесора Cortex-M4.

8- і 16-бітові типи даних

Cortex-M4 має 32-розрядні регістри даних. Багато додатків по обробці сигналу маніпулюють з 8- і 16-розрядних вибірками даних. 32-розрядні регістри дозволяють збільшити продуктивність за рахунок того, що вони можуть зберігати дві 16-розрядні або чотири 8-розрядні вибірки даних і працювати з такими форматами даних.

Процесор Cortex-M4 забезпечує широкий набір SIMD-функцій (Single Instruction, Multiple Data - одна інструкція, безліч даних), що гарантує виконання таких алгоритмів за мінімальне число тактів процесора. За допомогою SIMD-функцій чисельні операції можуть бути одночасно застосовані до двох 16-бітовим або чотирьом 8-бітовим значенням.

SIMD-арифметика

Процесор Cortex-M4 має можливість виконувати арифметичні операції над упакованими 8- і 16-бітовими даними. Різні варіанти цих команд показані в таблиці 3. Є і інші потужні команди, які дозволяють змінювати півслова в другому регістрі операнда і виконувати різні операції з півслова. Є також команди складання різниці без знака, які можуть працювати з пиксельними даними зображень і вельми корисні в таких додатках як розрахунок траєкторії руху.

Таблиця 3. Арифметичні SIMD-операції процесора Cortex-M4

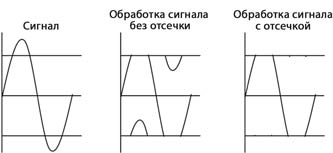

Математичні операції з відсіченням

Значення вибірки даних в алгоритмах обробки сигналу з фіксованою точкою повинні залишатися в межах чітко заданого діапазону чисел. Якщо числа виходять занадто маленькими, то ефект шуму квантування погіршує продуктивність. Якщо числа занадто великі, то виникає ймовірність переповнення. Алгоритми з фіксованою точкою вимагають ретельного масштабування і майже завжди розробляються з урахуванням можливого переповнення при певних умовах. Стандартна целочисленная арифметика обробляє переповнення найгіршим з можливих способів: виконується циклічне звернення до значення вибірки по переповнення, що призводить до порушення безперервності сигналу. Для зменшення цього ефекту в процесорі Cortex-M4 передбачені математичні операції з відсіченням. Коли значення вибірки переповнюється, то воно обрізається до максимального позитивного або негативного значень. Відсічення відбувається в тому ж циклі, що і арифметична операція, і не тягне за собою непродуктивних витрат (див. Рис. 3).

Мал. 3. Обробка сигналу з відсіченням

Многорегістровое пристрій циклічного зсуву

Операції зсуву також вельми поширені в DSP-алгоритмах з фіксованою точкою. Зрушення використовується, наприклад, для того, щоб забезпечити додаткові біти захисту від переповнення. Більшість пристроїв можуть, як правило, зрушувати значення на один біт вліво або вправо, але часто потрібні багаторазово повторювані операції зсуву. У процесорі Cortex-M4 передбачений зрушення даних на довільне число біт вліво або вправо за один такт, що покращує ефективність коду.

Реалізація апаратних засобів в МК, якими не можна просто і зручно користуватися, є марною справою. Простота програмування має вирішальне значення для швидкого освоєння високопродуктивних апаратних засобів. Протягом багатьох років робилися спроби зробити Мікроконтроллерні технологію доступною для масового ринку за допомогою вельми зручних у використанні програмних інструментів розробки для створення складних додатків. Процесор Cortex-M4 і його програмна екосистема підтримки також спрямовані на вдосконалення принципу простоти використання при створенні функцій обробки сигналу, які традиційно вважалися важкореалізованими.

Програмні інструменти розробки

Інтегровані функції обробки сигналу процесора Cortex-M4 спрощують розробку прикладного програмного забезпечення завдяки використанню одного пакета інструментів для пристрою обробки в порівнянні з архітектурою, в яких використовуються окремі прикладні процесори разом з програмованими DSP або прискорювачами з фіксованими функціями. Єдине середовище інструментів розробки прискорює час виведення продукту на ринок, оскільки ПО грає все більш важливу роль в розробці системи.

Багато високопродуктивних операції обробки сигналу процесора Cortex-M4 можна поліпшити за допомогою компілятора. Там, де необхідно оптимізація коду, компілятори C забезпечують підтримку вбудованих функцій для реалізації низькорівневих операцій на асемблері. Вбудовані функції дозволяють максимально використовувати всі можливості програмування на асемблері в середовищі розробки мови C і в той же час уникати складності ассемблерного коду.

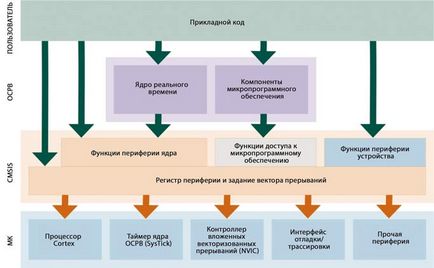

Стандарт програмного інтерфейсу МК Cortex (CMSIS)

Зазвичай стандарти використовують для того, щоб поліпшити якість продукту і забезпечити їх широке застосування в різних проектах. В електронній галузі є безліч таких стандартів, але на ринку МК є багато фірмових архітектур процесорів, в яких не можна застосовувати ефективні стандартні програмні засоби. Ця ситуація швидко змінюється в першу чергу через швидке впровадження процесорів ARM Cortex-M. Вперше галузь вбудованих МК отримала можливість стандартизації на базі єдиної популярної апаратної платформи.

Компанія ARM створила стандарт програмного інтерфейсу МК Cortex (Cortex Microcontroller Software Interface Standard - CMSIS), що дозволяє виробникам напівпровідників і постачальникам мікропрограм створювати ПО, яке можна легко інтегрувати в пристрої. Стандарт CMSIS був розроблений у тісній співпраці з кількома ключовими вендорами напівпровідників і ПО. CMSIS - це незалежний від виробника абстрактний рівень представлення апаратних засобів, який забезпечує єдиний підхід до об'єднання в пару периферії, ОСРВ і мікропрограмних компонентів (див. Рис. 4). Цей стандарт є масштабованим, що гарантує його придатність для всіх МК на базі процесорів сімейства Cortex-M - від молодших членів цього сімейства з 8-Кбайт пам'яттю до приладів зі складною комунікаційної периферією, такий як Ethernet або USB-OTG. CMSIS був розроблений як відкритий програмний стандарт, яким можуть користуватися всі.

Щоб зменшити непродуктивні витрати в часто запускаються циклах, існує метод розгортання циклу, який використовується компілятором, але може також застосовуватися вручну для поліпшення продуктивності. Це ефективний незалежний від мови метод оптимізації. У кожному циклі є непродуктивні витрати для перевірки лічильника циклу і збільшення його в кожній ітерації (3 такту в процесорі Cortex-M4). Розгортання циклу обробляє n індексів циклу за одну ітерацію, що зменшує витрати в n раз (див. Табл. 9). Як видно з таблиці, внутрішній цикл тепер займає 5,75 такту на кожен коефіцієнт фільтра.

Таблиця 9. Код розгортання внутрішнього циклу для розрахунку КИХ-фільтра

Розгортання циклу в 4 рази

Всього 5,75 такту на кожен коефіцієнт фільтра

sum + = coeffs [k] * state [stateIndex];

sum + = coeffs [k] * state [stateIndex];

sum + = coeffs [k] * state [stateIndex];

sum + = coeffs [k] * state [stateIndex];

непродуктивні витрати циклу

2 x 4 = 8 тактів

Таблиця 10. Застосування SIMD-команд для оптимізації коду внутрішнього циклу для розрахунку КИХ-фільтра

Всього 2,375 такту на кожен коефіцієнт фільтра

filtLen = filtLen <<2;

for (k = 0; k

sum = __SMLALD (c, s, sum);

sum = __SMLALD (c, s, sum);

sum = __SMLALD (c, s, sum);

Всього 19 тактів, або 2,375 такту на коефіцієнт

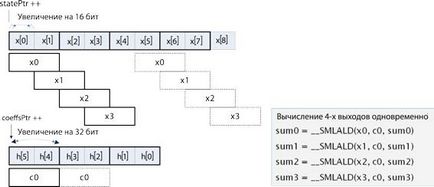

Обробка КИХ-фільтра вимагає досить частого звернення до пам'яті. 12 з 19 тактів в останній версії коду пов'язані зі зверненням до пам'яті. Наприклад, 2 послідовні завантаження вимагають три такту роботи процесора Cortex-M4, а MAC-команда вимагає тільки 1 такт. Коли обробляється блок даних, пропускна здатність пам'яті може бути поліпшена за рахунок одночасного розрахунку декількох виходів і кешування декількох коефіцієнтів і змінних стану. На малюнку 7 показана схема кешування проміжних змінних.

Мал. 7. Кешування проміжних змінних

Функції МК і DSP швидко зближуються, оскільки користувачам потрібні ефективні і прості у використанні технології обробки сигналу. Процесор Cortex-M4 від ARM надає відмінний спосіб реалізації пристроїв управління цифровими сигналами, призначених для таких додатків як управління електроприводами, промислова автоматика, що вбудовуються аудіосистеми, цифрове управління живленням і автомобільні додатки.

Процесор Cortex-M4 розширює сімейство процесорів Cortex-M на ринки цифрової обробки сигналу шляхом введення спеціальних DSP-функцій, подібних високопродуктивним однотактних командам множення з накопиченням, SIMD-арифметики, математичних операцій з відсіченням і блоків обчислень з плаваючою точкою одинарної точності.

Розробка додатків на процесорі Cortex-M4 проста і може бути виконана повністю на C. Використовуючи нескладні методи, можна розробити оптимізовані програми з мінімальними витратами і зусиллями на освоєння. Процесор Cortex-M4 - відмінний варіант для побудови систем на базі МК останнього покоління і цифрових сигнальних контролерів, оскільки такі системи призначені для додатків, що вимагають більш широких можливостей обробки сигналу.