Конфігураційна ПЗУ Altera типу EPCS програмується по JTAG інтерфейсу в режимі Active Serial за допомогою будь-якого з завантажувальних кабелів Altera, наприклад USB-Blaster, Byte-Blaster і для її прошивки використовується файл у форматі JTAG Indirect Configuration (.jic). Jic-файл можна сформувати з файлу конфігурації FPGA .sof в середовищі проектування Quartus. Для цього потрібно виконати наступні кроки:

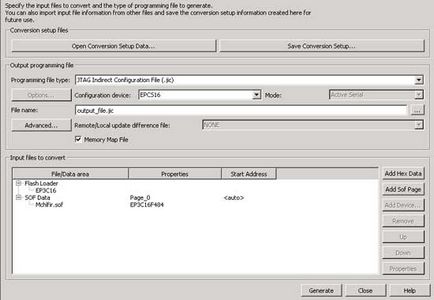

1. У головному меню File> Convert Progamming Files

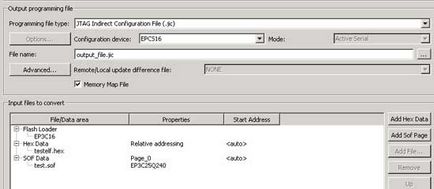

2. На панелі, що з'явилася вибираємо тип програмованого файлу як JTAG Indirect

Configuration File (.jic) from the Programming file type

3. В поле Configuration device вибрати тип девайса

4. У поле File name визначити ім'я і ДИРЕТОР вихідного .jic файлу

5. Клікнкть в поле SOF Data вікна Input files to convert

6. Клацнути Add File

7. Вира .sof файл який необхідно конвертувати в .jic

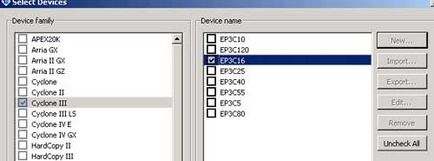

8. Підсвітити поле FlashLoader і клікнути на кнопку Add Device

9. На панелі вибрати необхідний FPGA девайс

10. Клінуть по кнопці Generate

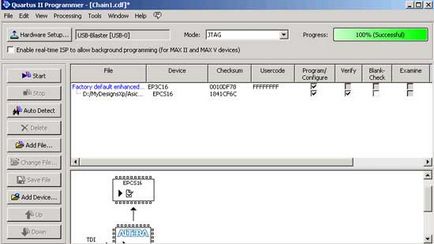

Далі підготовлений вище описаним способом .jic файл можна перенести власне в конфігураційну ПЗУ EPCS за допомогою Quartus програматора додавши в якості файлу програмування створений .jic файл.

Всі наведені вище дії описані в документі під назвою "Using the Serial FlashLoader with the Quartus II Software"

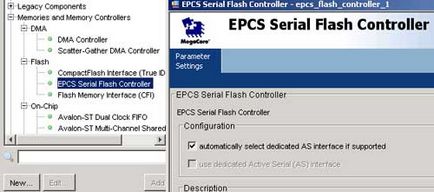

Отже припустимо створений і налагоджений проект з вбудованим процесором Nios II. При цьому будуть створені два файли з розширеннями .sof і .elf. Перший це конфігурація FPGA другий програма для Nios II. Для того, щоб створена система працювала автономно необхідно щоб .sof і .elf були розміщені в конфигурационной пам'яті один за одним і завантажувалися в потрібні місця FPGA і On-Chip (SDRAM) щодо включення харчування. Є кілька варіантів такого завантаження. Один з них, на мій погляд самий зручний, - використання в SOPC системі EPCS Serial Flash контролера, який має в своєму складі спеціальний завантажувач - програму яка запускається по включенню живлення. Завантажувач (або бутлоадер) виконує послідовно завантаження апаратної та програмних частин проекту і переводить вектор на початок програми.

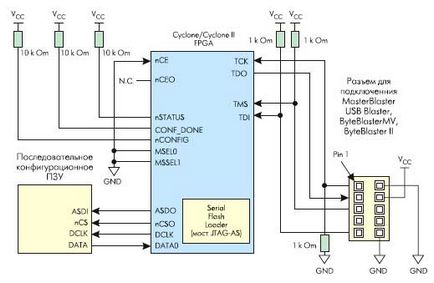

Схема підключення Flash девайса типу EPCS до FPGA нічим особливим не відрізняється. Стан входів Msel [1..0] визначає режим конфігурації Active Serial.

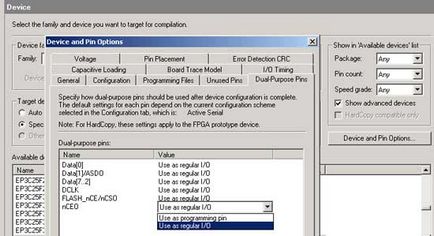

Єдине, що при призначенні ніжок необхідно встановити всі ніжки двойнго призначення як I / O. Для цього необхідно в меню Quartus вибрати Assigments> Device і клікнути на кнопку Device and Pin Options. На панелі, що з'явилася перейти на закладку Dual-Purpose Pins і виставити всі Піни як Use as regular I / O.

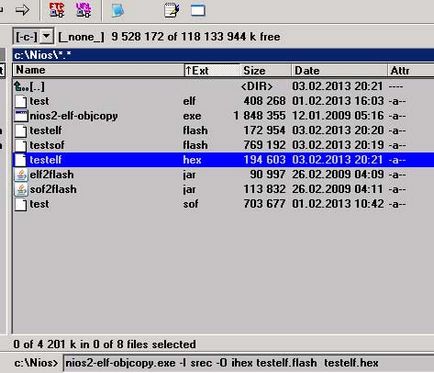

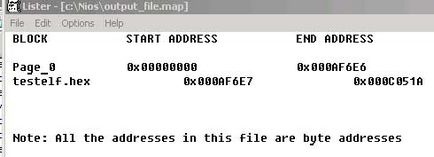

Тепер на базі файлів test.sof і testelf.hex можна створити .jic файл - образ для прошивки EPCS, який буде містити в собі образи конфігурації FPGA і програми Nios II наступними один за одним. Як описано на початку цього поста виконуємо кроки послідовно за пунктами по пункт номер 9. Далі:

10. Клінуть Add Hex Data і знаходимо файл конфігурації програмного проекту testelf.hex. Вказуємо у властивостях Hex Data Properties - Relative addressing.

11. Клацнути по кнопці Generate. Після успішного генерування .jic файлу кнфігураціі всього проекту егоможно прошивати в EPCS девайс за допомогою Quartus Programmer

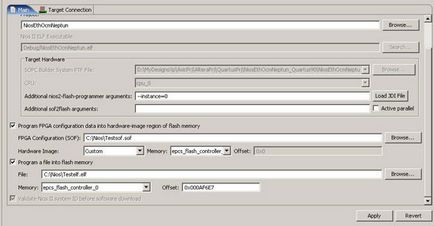

Якщо шановний Новомосковсктель подумав, що все, то немає. Не завжди від версії до версії Quartus такий варіант працює. Тобто після включення живлення проект не працює. Найкращий варіант це Nios II Flash Programer. З його допомогою можна прошити в девайс типу EPCS образи конфігурації FPGA і програми для Nios II (файли .sof і .elf) одним махом особливо не напружуючись. Найважливіше, що такий варіант повністю працездатний, тобто по включенню живлення модуль має в своєму складі FPGA (Nios II) + програму (працюючу наприклад в SDRAM) запускається і працює точно також як і в отладчике. Отже, вивчивши документ Nios II Flash Programmer User Guide:

Примітка: Всі вищеописане вироблялося на базі Quartus 9.0 В пізніших версіях Quartus програмування EPCS проводиться по тій-же технології з поправкою на приватні особливості версії.

Перейти і розтанути в своїй улюбленій соціалці